Loading...

Searching...

No Matches

x86_cpuid_info.c File Reference

Include dependency graph for x86_cpuid_info.c:

Go to the source code of this file.

Data Structures | |

| struct | _intel_cache_info |

Macros | |

| #define | TLB_SIZES 3 /* number of different page sizes for a single TLB descriptor */ |

Functions | |

| static void | init_mem_hierarchy (PAPI_mh_info_t *mh_info) |

| static int | init_amd (PAPI_mh_info_t *mh_info, int *levels) |

| static short int | _amd_L2_L3_assoc (unsigned short int pattern) |

| static int | init_intel (PAPI_mh_info_t *mh_info, int *levels) |

| static void | cpuid (unsigned int *a, unsigned int *b, unsigned int *c, unsigned int *d) |

| int | _x86_cache_info (PAPI_mh_info_t *mh_info) |

| static void | print_intel_cache_table () |

| static void | intel_decode_descriptor (struct _intel_cache_info *d, PAPI_mh_level_t *L) |

| static void | cpuid2 (unsigned int *eax, unsigned int *ebx, unsigned int *ecx, unsigned int *edx, unsigned int index, unsigned int ecx_in) |

| static int | init_intel_leaf4 (PAPI_mh_info_t *mh_info, int *num_levels) |

| static int | init_intel_leaf2 (PAPI_mh_info_t *mh_info, int *num_levels) |

| int | _x86_detect_hypervisor (char *vendor_name) |

Variables | |

| static struct _intel_cache_info | intel_cache [] |

Macro Definition Documentation

◆ TLB_SIZES

| #define TLB_SIZES 3 /* number of different page sizes for a single TLB descriptor */ |

Definition at line 359 of file x86_cpuid_info.c.

Function Documentation

◆ _amd_L2_L3_assoc()

Definition at line 115 of file x86_cpuid_info.c.

116{

117 /* From "CPUID Specification" #25481 Rev 2.28, April 2008 */

118 short int assoc[16] =

119 { 0, 1, 2, -1, 4, -1, 8, -1, 16, -1, 32, 48, 64, 96, 128, SHRT_MAX };

120 if ( pattern > 0xF )

121 return -1;

122 return ( assoc[pattern] );

123}

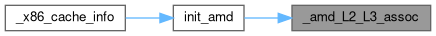

Here is the caller graph for this function:

◆ _x86_cache_info()

| int _x86_cache_info | ( | PAPI_mh_info_t * | mh_info | ) |

Definition at line 50 of file x86_cpuid_info.c.

51{

53 union

54 {

55 struct

56 {

57 unsigned int ax, bx, cx, dx;

58 } e;

59 char vendor[20]; /* leave room for terminator bytes */

60 } reg;

61

62 /* Don't use cpu_type to determine the processor.

63 * get the information directly from the chip.

64 */

65 reg.e.ax = 0; /* function code 0: vendor string */

66 /* The vendor string is composed of EBX:EDX:ECX.

67 * by swapping the register addresses in the call below,

68 * the string is correctly composed in the char array.

69 */

70 cpuid( ®.e.ax, ®.e.bx, ®.e.dx, ®.e.cx );

71 reg.vendor[16] = 0;

73

74 init_mem_hierarchy( mh_info );

75

76 if ( !strncmp( "GenuineIntel", ®.vendor[4], 12 ) ) {

78 } else if ( !strncmp( "AuthenticAMD", ®.vendor[4], 12 ) ) {

80 } else {

83 }

84

85 /* This works only because an empty cache element is initialized to 0 */

91}

static void cpuid(unsigned int *a, unsigned int *b, unsigned int *c, unsigned int *d)

Definition: x86_cpuid_info.c:35

static int init_intel(PAPI_mh_info_t *mh_info, int *levels)

Definition: x86_cpuid_info.c:1484

static void init_mem_hierarchy(PAPI_mh_info_t *mh_info)

Definition: x86_cpuid_info.c:94

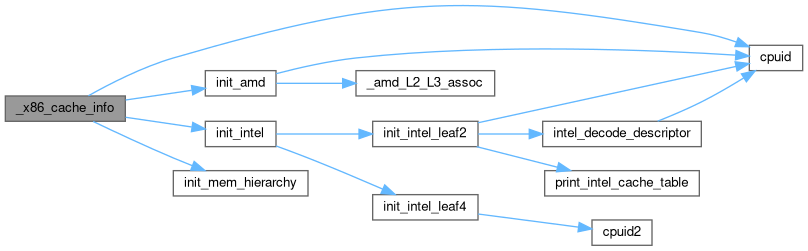

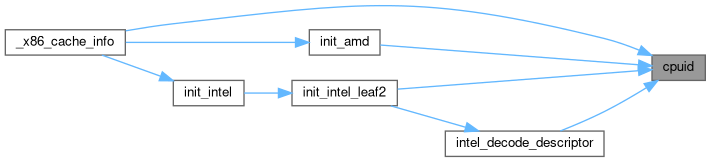

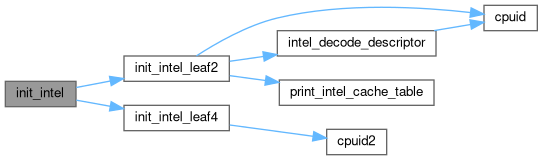

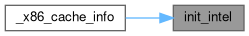

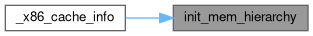

Here is the call graph for this function:

◆ _x86_detect_hypervisor()

| int _x86_detect_hypervisor | ( | char * | vendor_name | ) |

Definition at line 1507 of file x86_cpuid_info.c.

1508{

1509 unsigned int eax, ebx, ecx, edx;

1510 char hyper_vendor_id[13];

1511

1512 cpuid2(&eax, &ebx, &ecx, &edx,0x1,0);

1513 /* This is the hypervisor bit, ecx bit 31 */

1514 if (ecx&0x80000000) {

1515 /* There are various values in the 0x4000000X range */

1516 /* It is questionable how standard they are */

1517 /* For now we just return the name. */

1518 cpuid2(&eax, &ebx, &ecx, &edx, 0x40000000,0);

1519 memcpy(hyper_vendor_id + 0, &ebx, 4);

1520 memcpy(hyper_vendor_id + 4, &ecx, 4);

1521 memcpy(hyper_vendor_id + 8, &edx, 4);

1522 hyper_vendor_id[12] = '\0';

1523 strncpy(vendor_name,hyper_vendor_id,PAPI_MAX_STR_LEN);

1524 return 1;

1525 }

1526 else {

1528 }

1529 return 0;

1530}

static void cpuid2(unsigned int *eax, unsigned int *ebx, unsigned int *ecx, unsigned int *edx, unsigned int index, unsigned int ecx_in)

Definition: x86_cpuid_info.c:1272

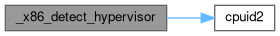

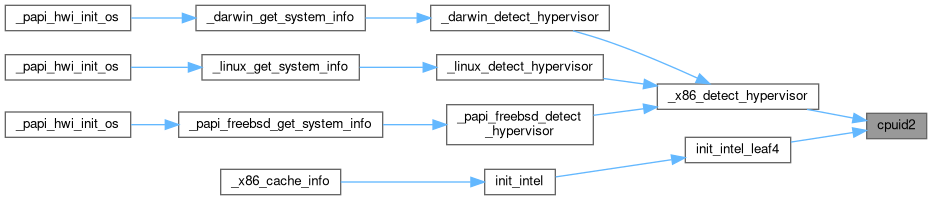

Here is the call graph for this function:

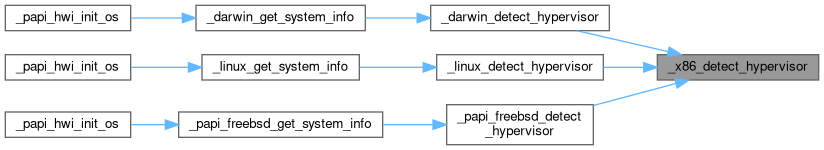

Here is the caller graph for this function:

◆ cpuid()

|

inlinestatic |

Definition at line 35 of file x86_cpuid_info.c.

36{

38 // .byte 0x53 == push ebx. it's universal for 32 and 64 bit

39 // .byte 0x5b == pop ebx.

40 // Some gcc's (4.1.2 on Core2) object to pairing push/pop and ebx in 64 bit mode.

41 // Using the opcode directly avoids this problem.

42 __asm__ __volatile__( ".byte 0x53\n\tcpuid\n\tmovl %%ebx, %%esi\n\t.byte 0x5b":"=a"( *a ), "=S"( *b ), "=c"( *c ),

43 "=d"

44 ( *d )

45 : "a"( op ) );

46}

Here is the caller graph for this function:

◆ cpuid2()

|

inlinestatic |

Definition at line 1272 of file x86_cpuid_info.c.

1275{

1277 __asm__ __volatile__ (".byte 0x53\n\tcpuid\n\tmovl %%ebx, %%esi\n\t.byte 0x5b"

1279 : "0" (index), "2"(ecx_in) );

1281}

Here is the caller graph for this function:

◆ init_amd()

|

static |

Definition at line 127 of file x86_cpuid_info.c.

128{

129 union

130 {

131 struct

132 {

133 unsigned int ax, bx, cx, dx;

134 } e;

135 unsigned char byt[16];

136 } reg;

139

140 /*

141 * Layout of CPU information taken from :

142 * "CPUID Specification" #25481 Rev 2.28, April 2008 for most current info.

143 */

144

146 /* AMD level 1 cache info */

147 reg.e.ax = 0x80000005; /* extended function code 5: L1 Cache and TLB Identifiers */

148 cpuid( ®.e.ax, ®.e.bx, ®.e.cx, ®.e.dx );

149

151 reg.e.ax, reg.e.bx, reg.e.cx, reg.e.dx );

152 MEMDBG

153 ( ":\neax: %#x %#x %#x %#x\nebx: %#x %#x %#x %#x\necx: %#x %#x %#x %#x\nedx: %#x %#x %#x %#x\n",

154 reg.byt[0], reg.byt[1], reg.byt[2], reg.byt[3], reg.byt[4],

155 reg.byt[5], reg.byt[6], reg.byt[7], reg.byt[8], reg.byt[9],

156 reg.byt[10], reg.byt[11], reg.byt[12], reg.byt[13], reg.byt[14],

157 reg.byt[15] );

158

159 /* NOTE: We assume L1 cache and TLB always exists */

160 /* L1 TLB info */

161

162 /* 4MB memory page information; half the number of entries as 2MB */

167

172

173 /* 2MB memory page information */

178

183

184 /* 4k page information */

189

194

198 }

199

200 /* L1 D-cache info */

206 /* Byt[9] is "Lines per tag" */

207 /* Is that == lines per cache? */

208 /* L[0].cache[1].num_lines = reg.byt[9]; */

209 if ( L[0].cache[0].line_size )

212 L[0].cache[0].num_lines );

213

214 /* L1 I-cache info */

219 /* Byt[13] is "Lines per tag" */

220 /* Is that == lines per cache? */

221 /* L[0].cache[1].num_lines = reg.byt[13]; */

222 if ( L[0].cache[1].line_size )

225 L[0].cache[1].num_lines );

226

230 }

231

232 /* AMD L2/L3 Cache and L2 TLB info */

233 /* NOTE: For safety we assume L2 and L3 cache and TLB may not exist */

234

235 reg.e.ax = 0x80000006; /* extended function code 6: L2/L3 Cache and L2 TLB Identifiers */

236 cpuid( ®.e.ax, ®.e.bx, ®.e.cx, ®.e.dx );

237

239 reg.e.ax, reg.e.bx, reg.e.cx, reg.e.dx );

240 MEMDBG

241 ( ":\neax: %#x %#x %#x %#x\nebx: %#x %#x %#x %#x\necx: %#x %#x %#x %#x\nedx: %#x %#x %#x %#x\n",

242 reg.byt[0], reg.byt[1], reg.byt[2], reg.byt[3], reg.byt[4],

243 reg.byt[5], reg.byt[6], reg.byt[7], reg.byt[8], reg.byt[9],

244 reg.byt[10], reg.byt[11], reg.byt[12], reg.byt[13], reg.byt[14],

245 reg.byt[15] );

246

247 /* L2 TLB info */

248

249 if ( reg.byt[0] | reg.byt[1] ) { /* Level 2 ITLB exists */

250 /* 4MB ITLB page information; half the number of entries as 2MB */

253 ( ( ( short ) ( reg.byt[1] & 0xF ) << 8 ) + reg.byt[0] ) / 2;

256 _amd_L2_L3_assoc( ( reg.byt[1] & 0xF0 ) >> 4 );

257

258 /* 2MB ITLB page information */

263 }

264

265 if ( reg.byt[2] | reg.byt[3] ) { /* Level 2 DTLB exists */

266 /* 4MB DTLB page information; half the number of entries as 2MB */

269 ( ( ( short ) ( reg.byt[3] & 0xF ) << 8 ) + reg.byt[2] ) / 2;

272 _amd_L2_L3_assoc( ( reg.byt[3] & 0xF0 ) >> 4 );

273

274 /* 2MB DTLB page information */

279 }

280

281 /* 4k page information */

282 if ( reg.byt[4] | reg.byt[5] ) { /* Level 2 ITLB exists */

285 ( ( short ) ( reg.byt[5] & 0xF ) << 8 ) + reg.byt[4];

286 L[1].tlb[4].page_size = 4 << 10;

287 L[1].tlb[4].associativity =

288 _amd_L2_L3_assoc( ( reg.byt[5] & 0xF0 ) >> 4 );

289 }

290 if ( reg.byt[6] | reg.byt[7] ) { /* Level 2 DTLB exists */

293 ( ( short ) ( reg.byt[7] & 0xF ) << 8 ) + reg.byt[6];

294 L[1].tlb[5].page_size = 4 << 10;

295 L[1].tlb[5].associativity =

296 _amd_L2_L3_assoc( ( reg.byt[7] & 0xF0 ) >> 4 );

297 }

298

299 /* AMD Level 2 cache info */

300 if ( reg.e.cx ) {

303 L[1].cache[0].size = ( int ) ( ( reg.e.cx & 0xffff0000 ) >> 6 ); /* right shift by 16; multiply by 2^10 */

305 _amd_L2_L3_assoc( ( reg.byt[9] & 0xF0 ) >> 4 );

307/* L[1].cache[0].num_lines = reg.byt[9]&0xF; */

308 if ( L[1].cache[0].line_size )

312 L[1].cache[0].num_lines );

313 }

314

315 /* AMD Level 3 cache info (shared across cores) */

316 if ( reg.e.dx ) {

321 _amd_L2_L3_assoc( ( reg.byt[13] & 0xF0 ) >> 4 );

323/* L[2].cache[0].num_lines = reg.byt[13]&0xF; */

324 if ( L[2].cache[0].line_size )

328 L[1].cache[0].num_lines );

329 }

332 /* Compute the number of levels of hierarchy actually used */

335 levels = i + 1;

336 }

337 }

338 *num_levels = levels;

340}

Definition: papi.h:760

static short int _amd_L2_L3_assoc(unsigned short int pattern)

Definition: x86_cpuid_info.c:115

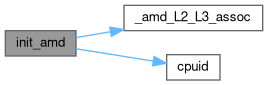

Here is the call graph for this function:

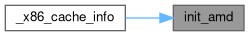

Here is the caller graph for this function:

◆ init_intel()

|

static |

Definition at line 1484 of file x86_cpuid_info.c.

1485{

1486

1488 int num_levels;

1489

1490 /* try using the oldest leaf2 method first */

1492

1494 /* All Core2 and newer also support leaf4 detection */

1495 /* Starting with Westmere *only* leaf4 is supported */

1497 }

1498

1499 *levels=num_levels;

1501}

static int init_intel_leaf2(PAPI_mh_info_t *mh_info, int *num_levels)

Definition: x86_cpuid_info.c:1395

static int init_intel_leaf4(PAPI_mh_info_t *mh_info, int *num_levels)

Definition: x86_cpuid_info.c:1286

Here is the call graph for this function:

Here is the caller graph for this function:

◆ init_intel_leaf2()

|

static |

Definition at line 1395 of file x86_cpuid_info.c.

1396{

1397 /* cpuid() returns memory copies of 4 32-bit registers

1398 * this union allows them to be accessed as either registers

1399 * or individual bytes. Remember that Intel is little-endian.

1400 */

1401 union

1402 {

1403 struct

1404 {

1405 unsigned int ax, bx, cx, dx;

1406 } e;

1407 unsigned char descrip[16];

1408 } reg;

1409

1410 int r; /* register boundary index */

1413 int t; /* table index into the static descriptor table */

1415 int size; /* size of the descriptor table */

1416 int last_level = 0; /* how many levels in the cache hierarchy */

1417

1418 /* All of Intel's cache info is in 1 call to cpuid

1419 * however it is a table lookup :(

1420 */

1422

1423#ifdef DEBUG

1425 print_intel_cache_table( );

1426#endif

1427

1428 reg.e.ax = 0x2; /* function code 2: cache descriptors */

1429 cpuid( ®.e.ax, ®.e.bx, ®.e.cx, ®.e.dx );

1430

1432 reg.e.ax, reg.e.bx, reg.e.cx, reg.e.dx );

1433 MEMDBG

1434 ( ":\nd0: %#x %#x %#x %#x\nd1: %#x %#x %#x %#x\nd2: %#x %#x %#x %#x\nd3: %#x %#x %#x %#x\n",

1435 reg.descrip[0], reg.descrip[1], reg.descrip[2], reg.descrip[3],

1436 reg.descrip[4], reg.descrip[5], reg.descrip[6], reg.descrip[7],

1437 reg.descrip[8], reg.descrip[9], reg.descrip[10], reg.descrip[11],

1438 reg.descrip[12], reg.descrip[13], reg.descrip[14], reg.descrip[15] );

1439

1441

1442 /* Knights Corner at least returns 0 here */

1444

1447 count );

1450 }

1451

1452 for ( r = 0; r < 4; r++ ) { /* walk the registers */

1453 if ( ( reg.descrip[r * 4 + 3] & 0x80 ) == 0 ) { /* only process if high order bit is 0 */

1460 /* we might continue instead */

1461 /* in order to get TLB info */

1462 /* continue; */

1463 }

1464 for ( t = 0; t < size; t++ ) { /* walk the descriptor table */

1469 mh_info->level );

1470 }

1471 }

1472 }

1473 }

1474 }

1475 }

1476early_exit:

1478 *num_levels=last_level;

1480}

FILE * stderr

Definition: x86_cpuid_info.c:361

static void intel_decode_descriptor(struct _intel_cache_info *d, PAPI_mh_level_t *L)

Definition: x86_cpuid_info.c:1210

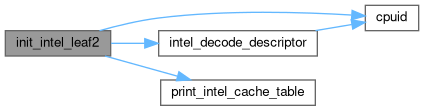

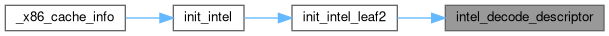

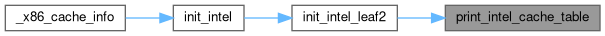

Here is the call graph for this function:

Here is the caller graph for this function:

◆ init_intel_leaf4()

|

static |

Definition at line 1286 of file x86_cpuid_info.c.

1287{

1288

1289 unsigned int eax, ebx, ecx, edx;

1290 unsigned int maxidx, ecx_in;

1291 int next;

1292

1293 int cache_type,cache_level,cache_selfinit,cache_fullyassoc;

1294 int cache_linesize,cache_partitions,cache_ways,cache_sets;

1295

1297

1298 *num_levels=0;

1299

1300 cpuid2(&eax,&ebx,&ecx,&edx, 0, 0);

1301 maxidx = eax;

1302

1303 if (maxidx<4) {

1306 }

1307

1308 ecx_in=0;

1309 while(1) {

1310 cpuid2(&eax,&ebx,&ecx,&edx, 4, ecx_in);

1311

1312

1313

1314 /* decoded as per table 3-12 in Intel Software Developer's Manual Volume 2A */

1315

1316 cache_type=eax&0x1f;

1317 if (cache_type==0) break;

1318

1319 cache_level=(eax>>5)&0x3;

1320 cache_selfinit=(eax>>8)&0x1;

1321 cache_fullyassoc=(eax>>9)&0x1;

1322

1323 cache_linesize=(ebx&0xfff)+1;

1324 cache_partitions=((ebx>>12)&0x3ff)+1;

1325 cache_ways=((ebx>>22)&0x3ff)+1;

1326

1327 cache_sets=(ecx)+1;

1328

1329 /* should we export this info?

1330

1331 cache_maxshare=((eax>>14)&0xfff)+1;

1332 cache_maxpackage=((eax>>26)&0x3f)+1;

1333

1334 cache_wb=(edx)&1;

1335 cache_inclusive=(edx>>1)&1;

1336 cache_indexing=(edx>>2)&1;

1337 */

1338

1339 if (cache_level>*num_levels) *num_levels=cache_level;

1340

1341 /* find next slot available to hold cache info */

1344 }

1345

1347

1348 switch(cache_type) {

1351 break;

1354 break;

1357 break;

1358 }

1359

1362

1363 //MEMDBG("\tMax logical processors sharing cache: %d\n",cache_maxshare);

1364 //MEMDBG("\tMax logical processors sharing package: %d\n",cache_maxpackage);

1365

1367

1370

1373 (cache_ways*cache_partitions*cache_linesize*cache_sets)/1024);

1374

1375 //MEMDBG("\tWBINVD/INVD acts on lower caches: %d\n",cache_wb);

1376 //MEMDBG("\tCache is not inclusive: %d\n",cache_inclusive);

1377 //MEMDBG("\tComplex cache indexing: %d\n",cache_indexing);

1378

1379 c->line_size=cache_linesize;

1380 if (cache_fullyassoc) {

1381 c->associativity=SHRT_MAX;

1382 }

1383 else {

1384 c->associativity=cache_ways;

1385 }

1386 c->size=(cache_ways*cache_partitions*cache_linesize*cache_sets);

1387 c->num_lines=cache_ways*cache_partitions*cache_sets;

1388

1389 ecx_in++;

1390 }

1392}

Definition: papi.h:751

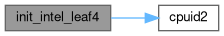

Here is the call graph for this function:

Here is the caller graph for this function:

◆ init_mem_hierarchy()

|

static |

Definition at line 94 of file x86_cpuid_info.c.

95{

98

99 /* initialize entire memory hierarchy structure to benign values */

110 }

111 }

112}

Here is the caller graph for this function:

◆ intel_decode_descriptor()

|

static |

Definition at line 1210 of file x86_cpuid_info.c.

1211{

1214 PAPI_mh_tlb_info_t *t;

1216

1218 unsigned int r_eax, r_ebx, r_ecx, r_edx;

1219 r_eax = 0x1; /* function code 1: family & model */

1220 cpuid( &r_eax, &r_ebx, &r_ecx, &r_edx );

1221 /* override table for Family F, model 6 only */

1222 if ( ( r_eax & 0x0FFF3FF0 ) == 0xF60 )

1223 level = 3;

1224 }

1228 break;

1229 }

1230 /* expand TLB entries for multiple possible page sizes */

1232 i++, next++ ) {

1233// printf("Level %d Descriptor: %#x TLB type %#x next: %d, i: %d\n", level, d->descriptor, d->type, next, i);

1234 t = &L[level].tlb[next];

1239 /* another special case */

1242 }

1243 } else {

1246 break;

1247 }

1248// printf("Level %d Descriptor: %#x Cache type %#x next: %d\n", level, d->descriptor, d->type, next);

1256 }

1257 }

1258}

Definition: papi.h:743

Here is the call graph for this function:

Here is the caller graph for this function:

◆ print_intel_cache_table()

|

static |

Definition at line 1183 of file x86_cpuid_info.c.

1184{

1192 printf( "\t Size(s): " );

1195 printf( "\n" );

1200 printf( "\n" );

1201 }

1202}

Here is the caller graph for this function:

Variable Documentation

◆ intel_cache

|

static |

Definition at line 372 of file x86_cpuid_info.c.