202{

203#define HAS_OPTIONS(x) (cntrs && (cntrs[x].flags || cntrs[x].cnt_mask))

204#define is_fixed_pmc(a) (a == 16 || a == 17 || a == 18)

205

211 uint64_t val;

212 unsigned long plm;

213 unsigned long long fixed_ctr;

214 unsigned int npc, npmc0, npmc1, nf2;

215 unsigned int i, j, n, k, ucode, use_pebs = 0, done_pebs;

217 unsigned int next_gen, last_gen;

218

219 npc = npmc0 = npmc1 = nf2 = 0;

220

228

231

232

233

234

237

238

239

240

241 for(

i=0;

i < n;

i++) {

242

243

244

247

248

249

250

253

255 && e[

i].num_masks > 1) {

256 DPRINT(

"events does not support unit mask combination\n");

258 }

259

260

261

262

263

265 if (++npmc0 > 1) {

266 DPRINT(

"two events compete for a PMC0\n");

268 }

269 }

270

271

272

274 if (++npmc1 > 1) {

275 DPRINT(

"two events compete for a PMC1\n");

277 }

278 }

279

280

281

283 if (++nf2 > 1) {

284 DPRINT(

"two events compete for FIXED_CTR2\n");

286 }

288 DPRINT(

"UNHALTED_REFERENCE_CYCLES only accepts anythr filter\n");

290 }

291 }

292

293

294

296 unsigned int flags;

297

299

301 if (++nf2 > 1) {

302 DPRINT(

"two events compete for FIXED_CTR2\n");

304 }

306 DPRINT(

"fixed counters do not support inversion/counter-mask\n");

308 }

309 }

310 }

311 }

312

313 next_gen = 0;

314 last_gen = 1;

315

316

317

318

319

320

321

322

323 done_pebs = 0;

324 for(

i=0;

i < n;

i++) {

330 next_gen = 1;

331 done_pebs = 1;

332 }

337 if (next_gen == 1)

338 next_gen = 2;

339 else

340 next_gen = 0;

341 }

342 }

343

344

345

346

347

348

349

350

351

352

354 if (fixed_ctr) {

355 for(

i=0;

i < n;

i++) {

356

359 continue;

361 continue;

362 }

365 fixed_ctr &= ~1;

366 }

369 fixed_ctr &= ~2;

370 }

373 fixed_ctr &= ~4;

374 }

375 }

376 }

377

378

379

380 for(

i=0;

i < n;

i++) {

381 if (assign_pc[

i] == -1) {

382 for(; next_gen <= last_gen; next_gen++) {

384 break;

385 }

386 if (next_gen <= last_gen)

387 assign_pc[

i] = next_gen++;

388 else {

389 DPRINT(

"cannot assign generic counters\n");

391 }

392 }

393 }

394 j = 0;

395

396

398 k = 0;

399 for (

i=0;

i < n ;

i++ ) {

401 continue;

402 val = 0;

403

406 val |= 1ULL;

408 val |= 2ULL;

410 val |= 4ULL;

411 val |= 1ULL << 3;

412

413 reg.

val |= val << ((assign_pc[

i]-16)<<2);

414 }

415

421

422 __pfm_vbprintf(

"[FIXED_CTRL(pmc%u)=0x%"PRIx64

" pmi0=1 en0=0x%"PRIx64

" any0=%d pmi1=1 en1=0x%"PRIx64

" any1=%d pmi2=1 en2=0x%"PRIx64

" any2=%d] ",

423 pc[npc].reg_num,

426 !!(reg.

val & 0x4ULL),

427 (reg.

val>>4) & 0x3ULL,

428 !!((reg.

val>>4) & 0x4ULL),

429 (reg.

val>>8) & 0x3ULL,

430 !!((reg.

val>>8) & 0x4ULL));

431

432 if ((fixed_ctr & 0x1) == 0)

434 if ((fixed_ctr & 0x2) == 0)

436 if ((fixed_ctr & 0x4) == 0)

439

440 npc++;

441

442 if ((fixed_ctr & 0x1) == 0)

444 if ((fixed_ctr & 0x2) == 0)

446 if ((fixed_ctr & 0x4) == 0)

448 }

449

450 for (

i=0;

i < n ;

i++ ) {

451

453 continue;

454

456

457

459

461

463

464 ucode = (val >> 8) & 0xff;

465

467 ucode |=

intel_atom_pe[e[

i].event].pme_umasks[e[

i].unit_masks[k]].pme_ucode;

468

469 val |= ucode << 8;

470

476

481

482 if (cntrs) {

484

485

486

487

488 if (cntrs[

i].cnt_mask > 255)

491 }

492

499 }

500

505

506 __pfm_vbprintf(

"[PERFEVTSEL%u(pmc%u)=0x%"PRIx64

" event_sel=0x%x umask=0x%x os=%d usr=%d en=%d int=%d inv=%d edge=%d cnt_mask=%d anythr=%d] %s\n",

507 pc[npc].reg_num,

508 pc[npc].reg_num,

521

523 pc[npc].reg_num,

524 pc[npc].reg_num);

525

526 npc++;

527 }

528

529

530

531 for (

i=0;

i < n ;

i++) {

533

537 } else {

540

542 }

543 }

545

546

547

548

549 if (use_pebs && done_pebs) {

550

551

552

559

561 pc[npc].reg_num,

562 pc[npc].reg_value,

563 pc[npc].reg_value & 0x1ull);

564

565 npc++;

566

567 }

569

571}

static pme_intel_atom_entry_t intel_atom_pe[]

#define PFMLIB_ERR_TOOMANY

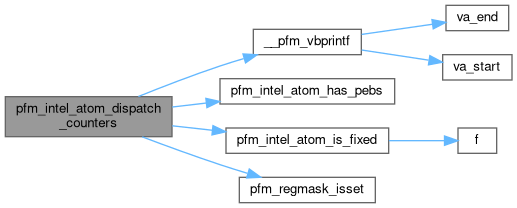

static int pfm_regmask_isset(pfmlib_regmask_t *h, unsigned int b)

#define PFMLIB_ERR_NOASSIGN

#define INTEL_ATOM_SEL_BASE

#define INTEL_ATOM_CTR_BASE

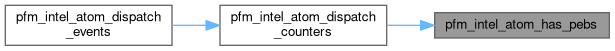

int pfm_intel_atom_has_pebs(pfmlib_event_t *e)

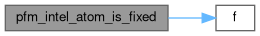

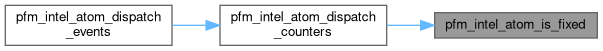

static int pfm_intel_atom_is_fixed(pfmlib_event_t *e, unsigned int f)

#define PFMLIB_INTEL_ATOM_ALL_FLAGS

#define PMU_INTEL_ATOM_NUM_COUNTERS

#define PFM_INTEL_ATOM_SEL_ANYTHR

#define PFM_INTEL_ATOM_SEL_EDGE

#define PFM_INTEL_ATOM_SEL_INV

#define PFMLIB_INTEL_ATOM_PMC0

#define PFMLIB_INTEL_ATOM_UMASK_NCOMBO

#define PFMLIB_INTEL_ATOM_FIXED2_ONLY

#define PFMLIB_INTEL_ATOM_PMC1

void __pfm_vbprintf(const char *fmt,...)

#define DPRINT(fmt, a...)

unsigned int unit_masks[PFMLIB_MAX_MASKS_PER_EVENT]

pfmlib_reg_t pfp_pmds[PFMLIB_MAX_PMDS]

pfmlib_reg_t pfp_pmcs[PFMLIB_MAX_PMCS]

unsigned int pfp_pmc_count

unsigned int pfp_pmd_count

unsigned long long reg_value

unsigned long reg_alt_addr

unsigned long long reg_addr

pme_intel_atom_umask_t pme_umasks[PFMLIB_INTEL_ATOM_MAX_UMASK]

unsigned long sel_event_select

unsigned long sel_cnt_mask

unsigned long sel_unit_mask