Loading...

Searching...

No Matches

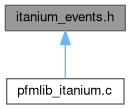

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Variables | |

| static pme_ita_entry_t | itanium_pe [] |

Macro Definition Documentation

◆ PME_ITA_ALAT_INST_CHKA_LDC_ALL

| #define PME_ITA_ALAT_INST_CHKA_LDC_ALL 0 |

◆ PME_ITA_ALAT_INST_CHKA_LDC_FP

| #define PME_ITA_ALAT_INST_CHKA_LDC_FP 1 |

◆ PME_ITA_ALAT_INST_CHKA_LDC_INT

| #define PME_ITA_ALAT_INST_CHKA_LDC_INT 2 |

◆ PME_ITA_ALAT_INST_FAILED_CHKA_LDC_ALL

| #define PME_ITA_ALAT_INST_FAILED_CHKA_LDC_ALL 3 |

◆ PME_ITA_ALAT_INST_FAILED_CHKA_LDC_FP

| #define PME_ITA_ALAT_INST_FAILED_CHKA_LDC_FP 4 |

◆ PME_ITA_ALAT_INST_FAILED_CHKA_LDC_INT

| #define PME_ITA_ALAT_INST_FAILED_CHKA_LDC_INT 5 |

◆ PME_ITA_ALAT_REPLACEMENT_ALL

| #define PME_ITA_ALAT_REPLACEMENT_ALL 6 |

◆ PME_ITA_ALAT_REPLACEMENT_FP

| #define PME_ITA_ALAT_REPLACEMENT_FP 7 |

◆ PME_ITA_ALAT_REPLACEMENT_INT

| #define PME_ITA_ALAT_REPLACEMENT_INT 8 |

◆ PME_ITA_ALL_STOPS_DISPERSED

| #define PME_ITA_ALL_STOPS_DISPERSED 9 |

◆ PME_ITA_BRANCH_EVENT

| #define PME_ITA_BRANCH_EVENT 10 |

◆ PME_ITA_BRANCH_MULTIWAY_ALL_PATHS_ALL_PREDICTIONS

| #define PME_ITA_BRANCH_MULTIWAY_ALL_PATHS_ALL_PREDICTIONS 11 |

◆ PME_ITA_BRANCH_MULTIWAY_ALL_PATHS_CORRECT_PREDICTIONS

| #define PME_ITA_BRANCH_MULTIWAY_ALL_PATHS_CORRECT_PREDICTIONS 12 |

◆ PME_ITA_BRANCH_MULTIWAY_ALL_PATHS_WRONG_PATH

| #define PME_ITA_BRANCH_MULTIWAY_ALL_PATHS_WRONG_PATH 13 |

◆ PME_ITA_BRANCH_MULTIWAY_ALL_PATHS_WRONG_TARGET

| #define PME_ITA_BRANCH_MULTIWAY_ALL_PATHS_WRONG_TARGET 14 |

◆ PME_ITA_BRANCH_MULTIWAY_NOT_TAKEN_ALL_PREDICTIONS

| #define PME_ITA_BRANCH_MULTIWAY_NOT_TAKEN_ALL_PREDICTIONS 15 |

◆ PME_ITA_BRANCH_MULTIWAY_NOT_TAKEN_CORRECT_PREDICTIONS

| #define PME_ITA_BRANCH_MULTIWAY_NOT_TAKEN_CORRECT_PREDICTIONS 16 |

◆ PME_ITA_BRANCH_MULTIWAY_NOT_TAKEN_WRONG_PATH

| #define PME_ITA_BRANCH_MULTIWAY_NOT_TAKEN_WRONG_PATH 17 |

◆ PME_ITA_BRANCH_MULTIWAY_NOT_TAKEN_WRONG_TARGET

| #define PME_ITA_BRANCH_MULTIWAY_NOT_TAKEN_WRONG_TARGET 18 |

◆ PME_ITA_BRANCH_MULTIWAY_TAKEN_ALL_PREDICTIONS

| #define PME_ITA_BRANCH_MULTIWAY_TAKEN_ALL_PREDICTIONS 19 |

◆ PME_ITA_BRANCH_MULTIWAY_TAKEN_CORRECT_PREDICTIONS

| #define PME_ITA_BRANCH_MULTIWAY_TAKEN_CORRECT_PREDICTIONS 20 |

◆ PME_ITA_BRANCH_MULTIWAY_TAKEN_WRONG_PATH

| #define PME_ITA_BRANCH_MULTIWAY_TAKEN_WRONG_PATH 21 |

◆ PME_ITA_BRANCH_MULTIWAY_TAKEN_WRONG_TARGET

| #define PME_ITA_BRANCH_MULTIWAY_TAKEN_WRONG_TARGET 22 |

◆ PME_ITA_BRANCH_NOT_TAKEN

| #define PME_ITA_BRANCH_NOT_TAKEN 23 |

◆ PME_ITA_BRANCH_PATH_1ST_STAGE_NT_OUTCOMES_CORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_1ST_STAGE_NT_OUTCOMES_CORRECTLY_PREDICTED 24 |

◆ PME_ITA_BRANCH_PATH_1ST_STAGE_NT_OUTCOMES_INCORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_1ST_STAGE_NT_OUTCOMES_INCORRECTLY_PREDICTED 25 |

◆ PME_ITA_BRANCH_PATH_1ST_STAGE_TK_OUTCOMES_CORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_1ST_STAGE_TK_OUTCOMES_CORRECTLY_PREDICTED 26 |

◆ PME_ITA_BRANCH_PATH_1ST_STAGE_TK_OUTCOMES_INCORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_1ST_STAGE_TK_OUTCOMES_INCORRECTLY_PREDICTED 27 |

◆ PME_ITA_BRANCH_PATH_2ND_STAGE_NT_OUTCOMES_CORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_2ND_STAGE_NT_OUTCOMES_CORRECTLY_PREDICTED 28 |

◆ PME_ITA_BRANCH_PATH_2ND_STAGE_NT_OUTCOMES_INCORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_2ND_STAGE_NT_OUTCOMES_INCORRECTLY_PREDICTED 29 |

◆ PME_ITA_BRANCH_PATH_2ND_STAGE_TK_OUTCOMES_CORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_2ND_STAGE_TK_OUTCOMES_CORRECTLY_PREDICTED 30 |

◆ PME_ITA_BRANCH_PATH_2ND_STAGE_TK_OUTCOMES_INCORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_2ND_STAGE_TK_OUTCOMES_INCORRECTLY_PREDICTED 31 |

◆ PME_ITA_BRANCH_PATH_3RD_STAGE_NT_OUTCOMES_CORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_3RD_STAGE_NT_OUTCOMES_CORRECTLY_PREDICTED 32 |

◆ PME_ITA_BRANCH_PATH_3RD_STAGE_NT_OUTCOMES_INCORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_3RD_STAGE_NT_OUTCOMES_INCORRECTLY_PREDICTED 33 |

◆ PME_ITA_BRANCH_PATH_3RD_STAGE_TK_OUTCOMES_CORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_3RD_STAGE_TK_OUTCOMES_CORRECTLY_PREDICTED 34 |

◆ PME_ITA_BRANCH_PATH_3RD_STAGE_TK_OUTCOMES_INCORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_3RD_STAGE_TK_OUTCOMES_INCORRECTLY_PREDICTED 35 |

◆ PME_ITA_BRANCH_PATH_ALL_NT_OUTCOMES_CORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_ALL_NT_OUTCOMES_CORRECTLY_PREDICTED 36 |

◆ PME_ITA_BRANCH_PATH_ALL_NT_OUTCOMES_INCORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_ALL_NT_OUTCOMES_INCORRECTLY_PREDICTED 37 |

◆ PME_ITA_BRANCH_PATH_ALL_TK_OUTCOMES_CORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_ALL_TK_OUTCOMES_CORRECTLY_PREDICTED 38 |

◆ PME_ITA_BRANCH_PATH_ALL_TK_OUTCOMES_INCORRECTLY_PREDICTED

| #define PME_ITA_BRANCH_PATH_ALL_TK_OUTCOMES_INCORRECTLY_PREDICTED 39 |

◆ PME_ITA_BRANCH_PREDICTOR_1ST_STAGE_ALL_PREDICTIONS

| #define PME_ITA_BRANCH_PREDICTOR_1ST_STAGE_ALL_PREDICTIONS 40 |

◆ PME_ITA_BRANCH_PREDICTOR_1ST_STAGE_CORRECT_PREDICTIONS

| #define PME_ITA_BRANCH_PREDICTOR_1ST_STAGE_CORRECT_PREDICTIONS 41 |

◆ PME_ITA_BRANCH_PREDICTOR_1ST_STAGE_WRONG_PATH

| #define PME_ITA_BRANCH_PREDICTOR_1ST_STAGE_WRONG_PATH 42 |

◆ PME_ITA_BRANCH_PREDICTOR_1ST_STAGE_WRONG_TARGET

| #define PME_ITA_BRANCH_PREDICTOR_1ST_STAGE_WRONG_TARGET 43 |

◆ PME_ITA_BRANCH_PREDICTOR_2ND_STAGE_ALL_PREDICTIONS

| #define PME_ITA_BRANCH_PREDICTOR_2ND_STAGE_ALL_PREDICTIONS 44 |

◆ PME_ITA_BRANCH_PREDICTOR_2ND_STAGE_CORRECT_PREDICTIONS

| #define PME_ITA_BRANCH_PREDICTOR_2ND_STAGE_CORRECT_PREDICTIONS 45 |

◆ PME_ITA_BRANCH_PREDICTOR_2ND_STAGE_WRONG_PATH

| #define PME_ITA_BRANCH_PREDICTOR_2ND_STAGE_WRONG_PATH 46 |

◆ PME_ITA_BRANCH_PREDICTOR_2ND_STAGE_WRONG_TARGET

| #define PME_ITA_BRANCH_PREDICTOR_2ND_STAGE_WRONG_TARGET 47 |

◆ PME_ITA_BRANCH_PREDICTOR_3RD_STAGE_ALL_PREDICTIONS

| #define PME_ITA_BRANCH_PREDICTOR_3RD_STAGE_ALL_PREDICTIONS 48 |

◆ PME_ITA_BRANCH_PREDICTOR_3RD_STAGE_CORRECT_PREDICTIONS

| #define PME_ITA_BRANCH_PREDICTOR_3RD_STAGE_CORRECT_PREDICTIONS 49 |

◆ PME_ITA_BRANCH_PREDICTOR_3RD_STAGE_WRONG_PATH

| #define PME_ITA_BRANCH_PREDICTOR_3RD_STAGE_WRONG_PATH 50 |

◆ PME_ITA_BRANCH_PREDICTOR_3RD_STAGE_WRONG_TARGET

| #define PME_ITA_BRANCH_PREDICTOR_3RD_STAGE_WRONG_TARGET 51 |

◆ PME_ITA_BRANCH_PREDICTOR_ALL_ALL_PREDICTIONS

| #define PME_ITA_BRANCH_PREDICTOR_ALL_ALL_PREDICTIONS 52 |

◆ PME_ITA_BRANCH_PREDICTOR_ALL_CORRECT_PREDICTIONS

| #define PME_ITA_BRANCH_PREDICTOR_ALL_CORRECT_PREDICTIONS 53 |

◆ PME_ITA_BRANCH_PREDICTOR_ALL_WRONG_PATH

| #define PME_ITA_BRANCH_PREDICTOR_ALL_WRONG_PATH 54 |

◆ PME_ITA_BRANCH_PREDICTOR_ALL_WRONG_TARGET

| #define PME_ITA_BRANCH_PREDICTOR_ALL_WRONG_TARGET 55 |

◆ PME_ITA_BRANCH_TAKEN_SLOT_0

| #define PME_ITA_BRANCH_TAKEN_SLOT_0 56 |

◆ PME_ITA_BRANCH_TAKEN_SLOT_1

| #define PME_ITA_BRANCH_TAKEN_SLOT_1 57 |

◆ PME_ITA_BRANCH_TAKEN_SLOT_2

| #define PME_ITA_BRANCH_TAKEN_SLOT_2 58 |

◆ PME_ITA_BUS_ALL_ANY

| #define PME_ITA_BUS_ALL_ANY 59 |

◆ PME_ITA_BUS_ALL_IO

| #define PME_ITA_BUS_ALL_IO 60 |

◆ PME_ITA_BUS_ALL_SELF

| #define PME_ITA_BUS_ALL_SELF 61 |

◆ PME_ITA_BUS_BRQ_LIVE_REQ_HI

| #define PME_ITA_BUS_BRQ_LIVE_REQ_HI 62 |

◆ PME_ITA_BUS_BRQ_LIVE_REQ_LO

| #define PME_ITA_BUS_BRQ_LIVE_REQ_LO 63 |

◆ PME_ITA_BUS_BRQ_REQ_INSERTED

| #define PME_ITA_BUS_BRQ_REQ_INSERTED 64 |

◆ PME_ITA_BUS_BURST_ANY

| #define PME_ITA_BUS_BURST_ANY 65 |

◆ PME_ITA_BUS_BURST_IO

| #define PME_ITA_BUS_BURST_IO 66 |

◆ PME_ITA_BUS_BURST_SELF

| #define PME_ITA_BUS_BURST_SELF 67 |

◆ PME_ITA_BUS_HITM

| #define PME_ITA_BUS_HITM 68 |

◆ PME_ITA_BUS_IO_ANY

| #define PME_ITA_BUS_IO_ANY 69 |

◆ PME_ITA_BUS_IO_SELF

| #define PME_ITA_BUS_IO_SELF 72 |

◆ PME_ITA_BUS_IOQ_LIVE_REQ_HI

| #define PME_ITA_BUS_IOQ_LIVE_REQ_HI 70 |

◆ PME_ITA_BUS_IOQ_LIVE_REQ_LO

| #define PME_ITA_BUS_IOQ_LIVE_REQ_LO 71 |

◆ PME_ITA_BUS_LOCK_ANY

| #define PME_ITA_BUS_LOCK_ANY 73 |

◆ PME_ITA_BUS_LOCK_CYCLES_ANY

| #define PME_ITA_BUS_LOCK_CYCLES_ANY 74 |

◆ PME_ITA_BUS_LOCK_CYCLES_SELF

| #define PME_ITA_BUS_LOCK_CYCLES_SELF 75 |

◆ PME_ITA_BUS_LOCK_SELF

| #define PME_ITA_BUS_LOCK_SELF 76 |

◆ PME_ITA_BUS_MEMORY_ANY

| #define PME_ITA_BUS_MEMORY_ANY 77 |

◆ PME_ITA_BUS_MEMORY_IO

| #define PME_ITA_BUS_MEMORY_IO 78 |

◆ PME_ITA_BUS_MEMORY_SELF

| #define PME_ITA_BUS_MEMORY_SELF 79 |

◆ PME_ITA_BUS_PARTIAL_ANY

| #define PME_ITA_BUS_PARTIAL_ANY 80 |

◆ PME_ITA_BUS_PARTIAL_IO

| #define PME_ITA_BUS_PARTIAL_IO 81 |

◆ PME_ITA_BUS_PARTIAL_SELF

| #define PME_ITA_BUS_PARTIAL_SELF 82 |

◆ PME_ITA_BUS_RD_ALL_ANY

| #define PME_ITA_BUS_RD_ALL_ANY 83 |

◆ PME_ITA_BUS_RD_ALL_IO

| #define PME_ITA_BUS_RD_ALL_IO 84 |

◆ PME_ITA_BUS_RD_ALL_SELF

| #define PME_ITA_BUS_RD_ALL_SELF 85 |

◆ PME_ITA_BUS_RD_DATA_ANY

| #define PME_ITA_BUS_RD_DATA_ANY 86 |

◆ PME_ITA_BUS_RD_DATA_IO

| #define PME_ITA_BUS_RD_DATA_IO 87 |

◆ PME_ITA_BUS_RD_DATA_SELF

| #define PME_ITA_BUS_RD_DATA_SELF 88 |

◆ PME_ITA_BUS_RD_HIT

| #define PME_ITA_BUS_RD_HIT 89 |

◆ PME_ITA_BUS_RD_HITM

| #define PME_ITA_BUS_RD_HITM 90 |

◆ PME_ITA_BUS_RD_INVAL_ANY

| #define PME_ITA_BUS_RD_INVAL_ANY 91 |

◆ PME_ITA_BUS_RD_INVAL_BST_ANY

| #define PME_ITA_BUS_RD_INVAL_BST_ANY 92 |

◆ PME_ITA_BUS_RD_INVAL_BST_HITM

| #define PME_ITA_BUS_RD_INVAL_BST_HITM 93 |

◆ PME_ITA_BUS_RD_INVAL_BST_IO

| #define PME_ITA_BUS_RD_INVAL_BST_IO 94 |

◆ PME_ITA_BUS_RD_INVAL_BST_SELF

| #define PME_ITA_BUS_RD_INVAL_BST_SELF 95 |

◆ PME_ITA_BUS_RD_INVAL_HITM

| #define PME_ITA_BUS_RD_INVAL_HITM 96 |

◆ PME_ITA_BUS_RD_INVAL_IO

| #define PME_ITA_BUS_RD_INVAL_IO 97 |

◆ PME_ITA_BUS_RD_INVAL_SELF

| #define PME_ITA_BUS_RD_INVAL_SELF 98 |

◆ PME_ITA_BUS_RD_IO_ANY

| #define PME_ITA_BUS_RD_IO_ANY 99 |

◆ PME_ITA_BUS_RD_IO_SELF

| #define PME_ITA_BUS_RD_IO_SELF 100 |

◆ PME_ITA_BUS_RD_PRTL_ANY

| #define PME_ITA_BUS_RD_PRTL_ANY 101 |

◆ PME_ITA_BUS_RD_PRTL_IO

| #define PME_ITA_BUS_RD_PRTL_IO 102 |

◆ PME_ITA_BUS_RD_PRTL_SELF

| #define PME_ITA_BUS_RD_PRTL_SELF 103 |

◆ PME_ITA_BUS_SNOOP_STALL_CYCLES_ANY

| #define PME_ITA_BUS_SNOOP_STALL_CYCLES_ANY 107 |

◆ PME_ITA_BUS_SNOOP_STALL_CYCLES_SELF

| #define PME_ITA_BUS_SNOOP_STALL_CYCLES_SELF 108 |

◆ PME_ITA_BUS_SNOOPQ_REQ

| #define PME_ITA_BUS_SNOOPQ_REQ 104 |

◆ PME_ITA_BUS_SNOOPS_ANY

| #define PME_ITA_BUS_SNOOPS_ANY 105 |

◆ PME_ITA_BUS_SNOOPS_HITM_ANY

| #define PME_ITA_BUS_SNOOPS_HITM_ANY 106 |

◆ PME_ITA_BUS_WR_WB_ANY

| #define PME_ITA_BUS_WR_WB_ANY 109 |

◆ PME_ITA_BUS_WR_WB_IO

| #define PME_ITA_BUS_WR_WB_IO 110 |

◆ PME_ITA_BUS_WR_WB_SELF

| #define PME_ITA_BUS_WR_WB_SELF 111 |

◆ PME_ITA_CPU_CPL_CHANGES

| #define PME_ITA_CPU_CPL_CHANGES 112 |

◆ PME_ITA_CPU_CYCLES

| #define PME_ITA_CPU_CYCLES 113 |

◆ PME_ITA_DATA_ACCESS_CYCLE

| #define PME_ITA_DATA_ACCESS_CYCLE 114 |

◆ PME_ITA_DATA_EAR_CACHE_LAT1024

| #define PME_ITA_DATA_EAR_CACHE_LAT1024 115 |

◆ PME_ITA_DATA_EAR_CACHE_LAT128

| #define PME_ITA_DATA_EAR_CACHE_LAT128 116 |

◆ PME_ITA_DATA_EAR_CACHE_LAT16

| #define PME_ITA_DATA_EAR_CACHE_LAT16 117 |

◆ PME_ITA_DATA_EAR_CACHE_LAT2048

| #define PME_ITA_DATA_EAR_CACHE_LAT2048 118 |

◆ PME_ITA_DATA_EAR_CACHE_LAT256

| #define PME_ITA_DATA_EAR_CACHE_LAT256 119 |

◆ PME_ITA_DATA_EAR_CACHE_LAT32

| #define PME_ITA_DATA_EAR_CACHE_LAT32 120 |

◆ PME_ITA_DATA_EAR_CACHE_LAT4

| #define PME_ITA_DATA_EAR_CACHE_LAT4 121 |

◆ PME_ITA_DATA_EAR_CACHE_LAT512

| #define PME_ITA_DATA_EAR_CACHE_LAT512 122 |

◆ PME_ITA_DATA_EAR_CACHE_LAT64

| #define PME_ITA_DATA_EAR_CACHE_LAT64 123 |

◆ PME_ITA_DATA_EAR_CACHE_LAT8

| #define PME_ITA_DATA_EAR_CACHE_LAT8 124 |

◆ PME_ITA_DATA_EAR_CACHE_LAT_NONE

| #define PME_ITA_DATA_EAR_CACHE_LAT_NONE 125 |

◆ PME_ITA_DATA_EAR_EVENTS

| #define PME_ITA_DATA_EAR_EVENTS 126 |

◆ PME_ITA_DATA_EAR_TLB_L2

| #define PME_ITA_DATA_EAR_TLB_L2 127 |

◆ PME_ITA_DATA_EAR_TLB_SW

| #define PME_ITA_DATA_EAR_TLB_SW 128 |

◆ PME_ITA_DATA_EAR_TLB_VHPT

| #define PME_ITA_DATA_EAR_TLB_VHPT 129 |

◆ PME_ITA_DATA_REFERENCES_RETIRED

| #define PME_ITA_DATA_REFERENCES_RETIRED 130 |

◆ PME_ITA_DEPENDENCY_ALL_CYCLE

| #define PME_ITA_DEPENDENCY_ALL_CYCLE 131 |

◆ PME_ITA_DEPENDENCY_SCOREBOARD_CYCLE

| #define PME_ITA_DEPENDENCY_SCOREBOARD_CYCLE 132 |

◆ PME_ITA_DTC_MISSES

| #define PME_ITA_DTC_MISSES 133 |

◆ PME_ITA_DTLB_INSERTS_HPW

| #define PME_ITA_DTLB_INSERTS_HPW 134 |

◆ PME_ITA_DTLB_MISSES

| #define PME_ITA_DTLB_MISSES 135 |

◆ PME_ITA_EVENT_COUNT

| #define PME_ITA_EVENT_COUNT 230 |

Definition at line 495 of file itanium_events.h.

◆ PME_ITA_EXPL_STOPBITS

| #define PME_ITA_EXPL_STOPBITS 136 |

◆ PME_ITA_FP_FLUSH_TO_ZERO

| #define PME_ITA_FP_FLUSH_TO_ZERO 137 |

◆ PME_ITA_FP_OPS_RETIRED_HI

| #define PME_ITA_FP_OPS_RETIRED_HI 138 |

◆ PME_ITA_FP_OPS_RETIRED_LO

| #define PME_ITA_FP_OPS_RETIRED_LO 139 |

◆ PME_ITA_FP_SIR_FLUSH

| #define PME_ITA_FP_SIR_FLUSH 140 |

◆ PME_ITA_IA32_INST_RETIRED

| #define PME_ITA_IA32_INST_RETIRED 141 |

◆ PME_ITA_IA64_INST_RETIRED

| #define PME_ITA_IA64_INST_RETIRED 142 |

◆ PME_ITA_IA64_TAGGED_INST_RETIRED_PMC8

| #define PME_ITA_IA64_TAGGED_INST_RETIRED_PMC8 143 |

◆ PME_ITA_IA64_TAGGED_INST_RETIRED_PMC9

| #define PME_ITA_IA64_TAGGED_INST_RETIRED_PMC9 144 |

◆ PME_ITA_INST_ACCESS_CYCLE

| #define PME_ITA_INST_ACCESS_CYCLE 145 |

◆ PME_ITA_INST_DISPERSED

| #define PME_ITA_INST_DISPERSED 146 |

◆ PME_ITA_INST_FAILED_CHKS_RETIRED_ALL

| #define PME_ITA_INST_FAILED_CHKS_RETIRED_ALL 147 |

◆ PME_ITA_INST_FAILED_CHKS_RETIRED_FP

| #define PME_ITA_INST_FAILED_CHKS_RETIRED_FP 148 |

◆ PME_ITA_INST_FAILED_CHKS_RETIRED_INT

| #define PME_ITA_INST_FAILED_CHKS_RETIRED_INT 149 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT1024

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT1024 150 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT128

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT128 151 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT16

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT16 152 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT2048

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT2048 153 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT256

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT256 154 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT32

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT32 155 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT4

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT4 157 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT4096

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT4096 156 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT512

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT512 158 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT64

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT64 159 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT8

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT8 160 |

◆ PME_ITA_INSTRUCTION_EAR_CACHE_LAT_NONE

| #define PME_ITA_INSTRUCTION_EAR_CACHE_LAT_NONE 161 |

◆ PME_ITA_INSTRUCTION_EAR_EVENTS

| #define PME_ITA_INSTRUCTION_EAR_EVENTS 162 |

◆ PME_ITA_INSTRUCTION_EAR_TLB_SW

| #define PME_ITA_INSTRUCTION_EAR_TLB_SW 163 |

◆ PME_ITA_INSTRUCTION_EAR_TLB_VHPT

| #define PME_ITA_INSTRUCTION_EAR_TLB_VHPT 164 |

◆ PME_ITA_ISA_TRANSITIONS

| #define PME_ITA_ISA_TRANSITIONS 165 |

◆ PME_ITA_ISB_LINES_IN

| #define PME_ITA_ISB_LINES_IN 166 |

◆ PME_ITA_ITLB_INSERTS_HPW

| #define PME_ITA_ITLB_INSERTS_HPW 167 |

◆ PME_ITA_ITLB_MISSES_FETCH

| #define PME_ITA_ITLB_MISSES_FETCH 168 |

◆ PME_ITA_L1_OUTSTANDING_REQ_HI

| #define PME_ITA_L1_OUTSTANDING_REQ_HI 175 |

◆ PME_ITA_L1_OUTSTANDING_REQ_LO

| #define PME_ITA_L1_OUTSTANDING_REQ_LO 176 |

◆ PME_ITA_L1D_READ_FORCED_MISSES_RETIRED

| #define PME_ITA_L1D_READ_FORCED_MISSES_RETIRED 169 |

◆ PME_ITA_L1D_READ_MISSES_RETIRED

| #define PME_ITA_L1D_READ_MISSES_RETIRED 170 |

◆ PME_ITA_L1D_READS_RETIRED

| #define PME_ITA_L1D_READS_RETIRED 171 |

◆ PME_ITA_L1I_DEMAND_READS

| #define PME_ITA_L1I_DEMAND_READS 172 |

◆ PME_ITA_L1I_FILLS

| #define PME_ITA_L1I_FILLS 173 |

◆ PME_ITA_L1I_PREFETCH_READS

| #define PME_ITA_L1I_PREFETCH_READS 174 |

◆ PME_ITA_L2_DATA_REFERENCES_ALL

| #define PME_ITA_L2_DATA_REFERENCES_ALL 177 |

◆ PME_ITA_L2_DATA_REFERENCES_READS

| #define PME_ITA_L2_DATA_REFERENCES_READS 178 |

◆ PME_ITA_L2_DATA_REFERENCES_WRITES

| #define PME_ITA_L2_DATA_REFERENCES_WRITES 179 |

◆ PME_ITA_L2_FLUSH_DETAILS_ADDR_CONFLICT

| #define PME_ITA_L2_FLUSH_DETAILS_ADDR_CONFLICT 180 |

◆ PME_ITA_L2_FLUSH_DETAILS_ALL

| #define PME_ITA_L2_FLUSH_DETAILS_ALL 181 |

◆ PME_ITA_L2_FLUSH_DETAILS_BUS_REJECT

| #define PME_ITA_L2_FLUSH_DETAILS_BUS_REJECT 182 |

◆ PME_ITA_L2_FLUSH_DETAILS_FULL_FLUSH

| #define PME_ITA_L2_FLUSH_DETAILS_FULL_FLUSH 183 |

◆ PME_ITA_L2_FLUSH_DETAILS_ST_BUFFER

| #define PME_ITA_L2_FLUSH_DETAILS_ST_BUFFER 184 |

◆ PME_ITA_L2_FLUSHES

| #define PME_ITA_L2_FLUSHES 185 |

◆ PME_ITA_L2_INST_DEMAND_READS

| #define PME_ITA_L2_INST_DEMAND_READS 186 |

◆ PME_ITA_L2_INST_PREFETCH_READS

| #define PME_ITA_L2_INST_PREFETCH_READS 187 |

◆ PME_ITA_L2_MISSES

| #define PME_ITA_L2_MISSES 188 |

◆ PME_ITA_L2_REFERENCES

| #define PME_ITA_L2_REFERENCES 189 |

◆ PME_ITA_L3_LINES_REPLACED

| #define PME_ITA_L3_LINES_REPLACED 190 |

◆ PME_ITA_L3_MISSES

| #define PME_ITA_L3_MISSES 191 |

◆ PME_ITA_L3_READS_ALL_READS_ALL

| #define PME_ITA_L3_READS_ALL_READS_ALL 192 |

◆ PME_ITA_L3_READS_ALL_READS_HIT

| #define PME_ITA_L3_READS_ALL_READS_HIT 193 |

◆ PME_ITA_L3_READS_ALL_READS_MISS

| #define PME_ITA_L3_READS_ALL_READS_MISS 194 |

◆ PME_ITA_L3_READS_DATA_READS_ALL

| #define PME_ITA_L3_READS_DATA_READS_ALL 195 |

◆ PME_ITA_L3_READS_DATA_READS_HIT

| #define PME_ITA_L3_READS_DATA_READS_HIT 196 |

◆ PME_ITA_L3_READS_DATA_READS_MISS

| #define PME_ITA_L3_READS_DATA_READS_MISS 197 |

◆ PME_ITA_L3_READS_INST_READS_ALL

| #define PME_ITA_L3_READS_INST_READS_ALL 198 |

◆ PME_ITA_L3_READS_INST_READS_HIT

| #define PME_ITA_L3_READS_INST_READS_HIT 199 |

◆ PME_ITA_L3_READS_INST_READS_MISS

| #define PME_ITA_L3_READS_INST_READS_MISS 200 |

◆ PME_ITA_L3_REFERENCES

| #define PME_ITA_L3_REFERENCES 201 |

◆ PME_ITA_L3_WRITES_ALL_WRITES_ALL

| #define PME_ITA_L3_WRITES_ALL_WRITES_ALL 202 |

◆ PME_ITA_L3_WRITES_ALL_WRITES_HIT

| #define PME_ITA_L3_WRITES_ALL_WRITES_HIT 203 |

◆ PME_ITA_L3_WRITES_ALL_WRITES_MISS

| #define PME_ITA_L3_WRITES_ALL_WRITES_MISS 204 |

◆ PME_ITA_L3_WRITES_DATA_WRITES_ALL

| #define PME_ITA_L3_WRITES_DATA_WRITES_ALL 205 |

◆ PME_ITA_L3_WRITES_DATA_WRITES_HIT

| #define PME_ITA_L3_WRITES_DATA_WRITES_HIT 206 |

◆ PME_ITA_L3_WRITES_DATA_WRITES_MISS

| #define PME_ITA_L3_WRITES_DATA_WRITES_MISS 207 |

◆ PME_ITA_L3_WRITES_L2_WRITEBACK_ALL

| #define PME_ITA_L3_WRITES_L2_WRITEBACK_ALL 208 |

◆ PME_ITA_L3_WRITES_L2_WRITEBACK_HIT

| #define PME_ITA_L3_WRITES_L2_WRITEBACK_HIT 209 |

◆ PME_ITA_L3_WRITES_L2_WRITEBACK_MISS

| #define PME_ITA_L3_WRITES_L2_WRITEBACK_MISS 210 |

◆ PME_ITA_LOADS_RETIRED

| #define PME_ITA_LOADS_RETIRED 211 |

◆ PME_ITA_MEMORY_CYCLE

| #define PME_ITA_MEMORY_CYCLE 212 |

◆ PME_ITA_MISALIGNED_LOADS_RETIRED

| #define PME_ITA_MISALIGNED_LOADS_RETIRED 213 |

◆ PME_ITA_MISALIGNED_STORES_RETIRED

| #define PME_ITA_MISALIGNED_STORES_RETIRED 214 |

◆ PME_ITA_NOPS_RETIRED

| #define PME_ITA_NOPS_RETIRED 215 |

◆ PME_ITA_PIPELINE_ALL_FLUSH_CYCLE

| #define PME_ITA_PIPELINE_ALL_FLUSH_CYCLE 216 |

◆ PME_ITA_PIPELINE_BACKEND_FLUSH_CYCLE

| #define PME_ITA_PIPELINE_BACKEND_FLUSH_CYCLE 217 |

◆ PME_ITA_PIPELINE_FLUSH_ALL

| #define PME_ITA_PIPELINE_FLUSH_ALL 218 |

◆ PME_ITA_PIPELINE_FLUSH_DTC_FLUSH

| #define PME_ITA_PIPELINE_FLUSH_DTC_FLUSH 219 |

◆ PME_ITA_PIPELINE_FLUSH_IEU_FLUSH

| #define PME_ITA_PIPELINE_FLUSH_IEU_FLUSH 220 |

◆ PME_ITA_PIPELINE_FLUSH_L1D_WAYMP_FLUSH

| #define PME_ITA_PIPELINE_FLUSH_L1D_WAYMP_FLUSH 221 |

◆ PME_ITA_PIPELINE_FLUSH_OTHER_FLUSH

| #define PME_ITA_PIPELINE_FLUSH_OTHER_FLUSH 222 |

◆ PME_ITA_PREDICATE_SQUASHED_RETIRED

| #define PME_ITA_PREDICATE_SQUASHED_RETIRED 223 |

◆ PME_ITA_RSE_LOADS_RETIRED

| #define PME_ITA_RSE_LOADS_RETIRED 224 |

◆ PME_ITA_RSE_REFERENCES_RETIRED

| #define PME_ITA_RSE_REFERENCES_RETIRED 225 |

◆ PME_ITA_STORES_RETIRED

| #define PME_ITA_STORES_RETIRED 226 |

◆ PME_ITA_UC_LOADS_RETIRED

| #define PME_ITA_UC_LOADS_RETIRED 227 |

◆ PME_ITA_UC_STORES_RETIRED

| #define PME_ITA_UC_STORES_RETIRED 228 |

◆ PME_ITA_UNSTALLED_BACKEND_CYCLE

| #define PME_ITA_UNSTALLED_BACKEND_CYCLE 229 |

Variable Documentation

◆ itanium_pe

|

static |

Definition at line 34 of file itanium_events.h.