230{

232

235

240

241 switch(attr) {

242

245 break;

248 break;

251 break;

254 break;

257 break;

260 break;

263 break;

266 break;

269 break;

272 break;

275 break;

278 break;

281 break;

284 break;

287 break;

290 break;

292 *(

const char **) val = cpu_info->

name;

293 break;

296 break;

299 break;

302 break;

304 *(

unsigned int *) val = cpu_info->

sockets;

305 break;

307 *(

unsigned int *) val = cpu_info->

numas;

308 break;

310 *(

int *) val = cpu_info->

cores;

311 break;

314 break;

317 break;

321 break;

323 *(

unsigned int *) val = (cpu_info->

numa_memory[id] >> 10);

324 break;

325

327 *(unsigned long *) val = gpu_info->nvidia.uid;

328 break;

330 *(const char **) val = gpu_info->nvidia.name;

331 break;

333 *(unsigned int *) val = gpu_info->nvidia.warp_size;

334 break;

336 *(unsigned int *) val = gpu_info->nvidia.max_threads_per_block;

337 break;

339 *(unsigned int *) val = gpu_info->nvidia.max_blocks_per_multi_proc;

340 break;

342 *(unsigned int *) val = gpu_info->nvidia.max_shmmem_per_block;

343 break;

345 *(unsigned int *) val = gpu_info->nvidia.max_shmmem_per_multi_proc;

346 break;

348 *(unsigned int *) val = gpu_info->nvidia.max_block_dim_x;

349 break;

351 *(unsigned int *) val = gpu_info->nvidia.max_block_dim_y;

352 break;

354 *(unsigned int *) val = gpu_info->nvidia.max_block_dim_z;

355 break;

357 *(unsigned int *) val = gpu_info->nvidia.max_grid_dim_x;

358 break;

360 *(unsigned int *) val = gpu_info->nvidia.max_grid_dim_y;

361 break;

363 *(unsigned int *) val = gpu_info->nvidia.max_grid_dim_z;

364 break;

366 *(unsigned int *) val = gpu_info->nvidia.multi_processor_count;

367 break;

369 *(unsigned int *) val = gpu_info->nvidia.multi_kernel_per_ctx;

370 break;

372 *(unsigned int *) val = gpu_info->nvidia.can_map_host_mem;

373 break;

375 *(unsigned int *) val = gpu_info->nvidia.can_overlap_comp_and_data_xfer;

376 break;

378 *(unsigned int *) val = gpu_info->nvidia.unified_addressing;

379 break;

381 *(unsigned int *) val = gpu_info->nvidia.managed_memory;

382 break;

384 *(unsigned int *) val = gpu_info->nvidia.major;

385 break;

387 *(unsigned int *) val = gpu_info->nvidia.minor;

388 break;

389

391 *(unsigned long *) val = gpu_info->amd.uid;

392 break;

394 *(const char **) val = gpu_info->amd.name;

395 break;

397 *(unsigned int *) val = gpu_info->amd.simd_per_compute_unit;

398 break;

400 *(unsigned int *) val = gpu_info->amd.max_threads_per_workgroup;

401 break;

403 *(unsigned int *) val = gpu_info->amd.wavefront_size;

404 break;

406 *(unsigned int *) val = gpu_info->amd.max_waves_per_compute_unit;

407 break;

409 *(unsigned int *) val = gpu_info->amd.max_shmmem_per_workgroup;

410 break;

412 *(unsigned int *) val = gpu_info->amd.max_workgroup_dim_x;

413 break;

415 *(unsigned int *) val = gpu_info->amd.max_workgroup_dim_y;

416 break;

418 *(unsigned int *) val = gpu_info->amd.max_workgroup_dim_z;

419 break;

421 *(unsigned int *) val = gpu_info->amd.max_grid_dim_x;

422 break;

424 *(unsigned int *) val = gpu_info->amd.max_grid_dim_y;

425 break;

427 *(unsigned int *) val = gpu_info->amd.max_grid_dim_z;

428 break;

430 *(unsigned int *) val = gpu_info->amd.compute_unit_count;

431 break;

433 *(unsigned int *) val = gpu_info->amd.major;

434 break;

436 *(unsigned int *) val = gpu_info->amd.minor;

437 break;

438 default:

440 }

441

442 return papi_errno;

443}

#define PAPI_DEV_ATTR__ROCM_UINT_WG_DIM_Y

#define PAPI_DEV_ATTR__CUDA_UINT_THR_PER_BLK

#define PAPI_DEV_ATTR__CUDA_UINT_WARP_SIZE

#define PAPI_DEV_ATTR__CPU_UINT_L1D_CACHE_LINE_COUNT

#define PAPI_DEV_ATTR__ROCM_UINT_GRD_DIM_Y

#define PAPI_DEV_ATTR__ROCM_UINT_WAVE_PER_CU

#define PAPI_DEV_ATTR__CUDA_UINT_BLK_PER_SM

#define PAPI_DEV_ATTR__CUDA_ULONG_UID

#define PAPI_DEV_ATTR__CPU_UINT_FAMILY

#define PAPI_DEV_ATTR__CPU_UINT_SOCKET_COUNT

#define PAPI_DEV_ATTR__CPU_UINT_THR_PER_NUMA

#define PAPI_DEV_ATTR__CPU_UINT_L1I_CACHE_LINE_SIZE

#define PAPI_DEV_ATTR__CUDA_UINT_BLK_DIM_Z

#define PAPI_DEV_ATTR__ROCM_UINT_WAVEFRONT_SIZE

#define PAPI_DEV_ATTR__CUDA_UINT_UNIFIED_ADDR

#define PAPI_DEV_ATTR__CUDA_UINT_SM_COUNT

#define PAPI_DEV_ATTR__CPU_UINT_L3U_CACHE_ASSOC

#define PAPI_DEV_ATTR__CUDA_UINT_GRD_DIM_Y

#define PAPI_DEV_ATTR__CPU_UINT_L1I_CACHE_SIZE

#define PAPI_DEV_ATTR__CPU_UINT_L3U_CACHE_LINE_SIZE

#define PAPI_DEV_ATTR__CPU_UINT_THREAD_COUNT

#define PAPI_DEV_ATTR__CPU_UINT_NUMA_COUNT

#define PAPI_DEV_ATTR__CPU_UINT_L1I_CACHE_LINE_COUNT

#define PAPI_DEV_ATTR__CUDA_UINT_MANAGED_MEM

#define PAPI_DEV_ATTR__CPU_UINT_L3U_CACHE_SIZE

#define PAPI_DEV_ATTR__ROCM_UINT_COMP_CAP_MINOR

#define PAPI_DEV_ATTR__CPU_UINT_L2U_CACHE_SIZE

#define PAPI_DEV_ATTR__CUDA_UINT_BLK_DIM_Y

#define PAPI_DEV_ATTR__ROCM_CHAR_DEVICE_NAME

#define PAPI_DEV_ATTR__CUDA_UINT_SHM_PER_BLK

#define PAPI_DEV_ATTR__ROCM_UINT_WORKGROUP_SIZE

#define PAPI_DEV_ATTR__CPU_UINT_L2U_CACHE_LINE_COUNT

#define PAPI_DEV_ATTR__ROCM_UINT_COMP_CAP_MAJOR

#define PAPI_DEV_ATTR__CPU_CHAR_NAME

#define PAPI_DEV_ATTR__CUDA_UINT_GRD_DIM_X

#define PAPI_DEV_ATTR__ROCM_ULONG_UID

#define PAPI_DEV_ATTR__CPU_UINT_L3U_CACHE_LINE_COUNT

#define PAPI_DEV_ATTR__CUDA_UINT_MEMCPY_OVERLAP

#define PAPI_DEV_ATTR__ROCM_UINT_SHM_PER_WG

#define PAPI_DEV_ATTR__CUDA_UINT_COMP_CAP_MINOR

#define PAPI_DEV_ATTR__CUDA_UINT_MAP_HOST_MEM

#define PAPI_DEV_ATTR__CPU_UINT_L1D_CACHE_ASSOC

#define PAPI_DEV_ATTR__CUDA_UINT_SHM_PER_SM

#define PAPI_DEV_ATTR__CPU_UINT_STEPPING

#define PAPI_DEV_ATTR__ROCM_UINT_CU_COUNT

#define PAPI_DEV_ATTR__CPU_UINT_THR_NUMA_AFFINITY

#define PAPI_DEV_ATTR__CUDA_UINT_BLK_DIM_X

#define PAPI_DEV_ATTR__CPU_UINT_NUMA_MEM_SIZE

#define PAPI_DEV_ATTR__ROCM_UINT_SIMD_PER_CU

#define PAPI_DEV_ATTR__ROCM_UINT_WG_DIM_X

#define PAPI_DEV_ATTR__CUDA_UINT_MULTI_KERNEL

#define PAPI_DEV_ATTR__CPU_UINT_L2U_CACHE_ASSOC

#define PAPI_DEV_ATTR__CUDA_UINT_GRD_DIM_Z

#define PAPI_DEV_ATTR__ROCM_UINT_GRD_DIM_X

#define PAPI_DEV_ATTR__CPU_UINT_L1D_CACHE_SIZE

#define PAPI_DEV_ATTR__CPU_UINT_MODEL

#define PAPI_DEV_ATTR__ROCM_UINT_WG_DIM_Z

#define PAPI_DEV_ATTR__ROCM_UINT_GRD_DIM_Z

#define PAPI_DEV_ATTR__CPU_UINT_L2U_CACHE_LINE_SIZE

#define PAPI_DEV_ATTR__CPU_UINT_CORE_COUNT

#define PAPI_DEV_ATTR__CPU_UINT_L1I_CACHE_ASSOC

#define PAPI_DEV_ATTR__CPU_UINT_L1D_CACHE_LINE_SIZE

#define PAPI_DEV_ATTR__CUDA_CHAR_DEVICE_NAME

#define PAPI_DEV_ATTR__CUDA_UINT_COMP_CAP_MAJOR

PAPI_mh_cache_info_t cache[PAPI_MH_MAX_LEVELS]

_sysdetect_cache_level_info_t clevel[PAPI_MAX_MEM_HIERARCHY_LEVELS]

int numa_affinity[PAPI_MAX_NUM_THREADS]

char name[PAPI_MAX_STR_LEN]

int numa_memory[PAPI_MAX_NUM_NODES]

int num_threads_per_numa[PAPI_MAX_THREADS_PER_NUMA]

_sysdetect_dev_info_u * dev_info_arr

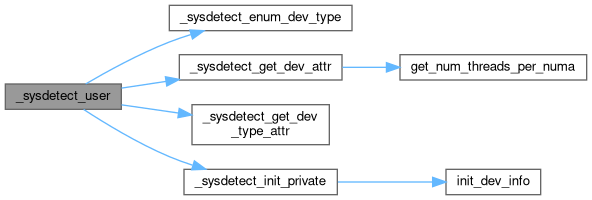

static void get_num_threads_per_numa(_sysdetect_cpu_info_t *cpu_info)