56{

57 static char mips_name[64] = "";

58 int ret;

59 char buffer[128];

60

62 if (ret == -1)

64

67 if (strstr(buffer,"MIPS 20Kc"))

68 {

75 }

76 else if (strstr(buffer,"MIPS 24K"))

77 {

84 }

85 else if (strstr(buffer,"MIPS 25Kf"))

86 {

93 }

94 else if (strstr(buffer,"MIPS 34K"))

95 {

102 }

103 else if (strstr(buffer,"MIPS 5Kc"))

104 {

111 }

112#if 0

113 else if (strstr(buffer,"MIPS 74K"))

114 {

121 }

122#endif

123 else if (strstr(buffer,"R10000"))

124 {

131 }

132 else if (strstr(buffer,"R12000"))

133 {

140 }

141 else if (strstr(buffer,"RM7000"))

142 {

149 }

150 else if (strstr(buffer,"RM9000"))

151 {

158 }

159 else if (strstr(buffer,"SB1"))

160 {

167 }

168 else if (strstr(buffer,"VR5432"))

169 {

176 }

177 else if (strstr(buffer,"VR5500"))

178 {

185 }

186 else

188

191

193}

static pme_gen_mips64_entry_t gen_mips64_r12000_pe[]

static pme_gen_mips64_entry_t gen_mips64_5K_pe[]

static pme_gen_mips64_entry_t gen_mips64_34K_pe[]

static pme_gen_mips64_entry_t gen_mips64_rm9000_pe[]

static pme_gen_mips64_entry_t gen_mips64_sb1_pe[]

static pme_gen_mips64_entry_t gen_mips64_r10000_pe[]

static pme_gen_mips64_entry_t gen_mips64_25K_pe[]

static pme_gen_mips64_entry_t gen_mips64_vr5500_pe[]

static pme_gen_mips64_entry_t gen_mips64_rm7000_pe[]

static pme_gen_mips64_entry_t gen_mips64_vr5432_pe[]

static pme_gen_mips64_entry_t gen_mips64_20K_pe[]

static pme_gen_mips64_entry_t gen_mips64_24K_pe[]

#define PFMLIB_MIPS_20KC_PMU

#define PFMLIB_MIPS_74K_PMU

#define PFMLIB_MIPS_SB1_PMU

#define PFMLIB_MIPS_R12000_PMU

#define PFMLIB_MIPS_25KF_PMU

#define PFMLIB_MIPS_RM9000_PMU

#define PFMLIB_MIPS_R10000_PMU

#define PFMLIB_MIPS_5KC_PMU

#define PFMLIB_MIPS_VR5500_PMU

#define PFMLIB_MIPS_24K_PMU

#define PFMLIB_MIPS_34K_PMU

#define PFMLIB_ERR_NOTSUPP

#define PFMLIB_MIPS_VR5432_PMU

#define PFMLIB_MIPS_RM7000_PMU

static pme_gen_mips64_entry_t * gen_mips64_pe

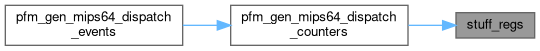

pfm_pmu_support_t generic_mips64_support

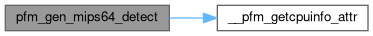

int __pfm_getcpuinfo_attr(const char *attr, char *ret_buf, size_t maxlen)