Loading...

Searching...

No Matches

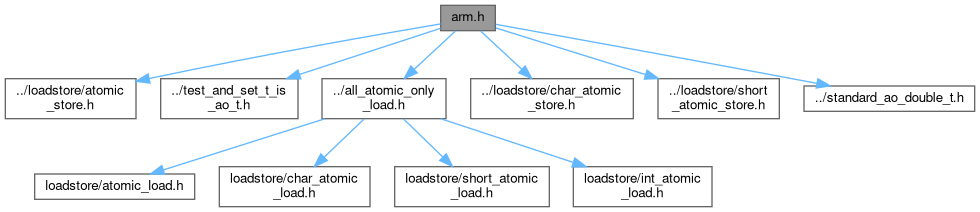

Include dependency graph for gcc/arm.h:

Go to the source code of this file.

Macros | |

| #define | AO_MASK_PTR(reg) /* empty */ |

| #define | AO_BR_ALIGN /* empty */ |

| #define | AO_THUMB_GO_ARM /* empty */ |

| #define | AO_THUMB_RESTORE_MODE /* empty */ |

| #define | AO_THUMB_SWITCH_CLOBBERS /* empty */ |

| #define | AO_ARM_HAVE_LDREX |

| #define | AO_ARM_HAVE_LDREXBH |

| #define | AO_ARM_HAVE_DMB |

| #define | AO_ARM_HAVE_LDREXD |

| #define | AO_ARM_HAVE_SWP |

| #define | AO_HAVE_nop_write |

| #define | AO_HAVE_nop_full |

| #define | AO_ACCESS_CHECK_ALIGNED |

| #define | AO_ACCESS_short_CHECK_ALIGNED |

| #define | AO_ACCESS_int_CHECK_ALIGNED |

| #define | AO_HAVE_test_and_set |

| #define | AO_HAVE_fetch_and_add |

| #define | AO_HAVE_fetch_and_add1 |

| #define | AO_HAVE_fetch_and_sub1 |

| #define | AO_HAVE_and |

| #define | AO_HAVE_or |

| #define | AO_HAVE_xor |

| #define | AO_HAVE_char_fetch_and_add |

| #define | AO_HAVE_short_fetch_and_add |

| #define | AO_HAVE_compare_and_swap |

| #define | AO_HAVE_fetch_compare_and_swap |

| #define | AO_HAVE_double_load |

| #define | AO_HAVE_double_store |

| #define | AO_HAVE_double_compare_and_swap |

| #define | AO_T_IS_INT |

Macro Definition Documentation

◆ AO_ACCESS_CHECK_ALIGNED

◆ AO_ACCESS_int_CHECK_ALIGNED

◆ AO_ACCESS_short_CHECK_ALIGNED

◆ AO_ARM_HAVE_DMB

◆ AO_ARM_HAVE_LDREX

◆ AO_ARM_HAVE_LDREXBH

◆ AO_ARM_HAVE_LDREXD

◆ AO_ARM_HAVE_SWP

◆ AO_BR_ALIGN

◆ AO_HAVE_and

◆ AO_HAVE_char_fetch_and_add

◆ AO_HAVE_compare_and_swap

◆ AO_HAVE_double_compare_and_swap

◆ AO_HAVE_double_load

◆ AO_HAVE_double_store

◆ AO_HAVE_fetch_and_add

◆ AO_HAVE_fetch_and_add1

◆ AO_HAVE_fetch_and_sub1

◆ AO_HAVE_fetch_compare_and_swap

◆ AO_HAVE_nop_full

◆ AO_HAVE_nop_write

◆ AO_HAVE_or

◆ AO_HAVE_short_fetch_and_add

◆ AO_HAVE_test_and_set

◆ AO_HAVE_xor

◆ AO_MASK_PTR

◆ AO_T_IS_INT

◆ AO_THUMB_GO_ARM

◆ AO_THUMB_RESTORE_MODE

◆ AO_THUMB_SWITCH_CLOBBERS

Function Documentation

◆ AO_and()

Definition at line 410 of file gcc/arm.h.

411{

413

414 __asm__ __volatile__("@AO_and\n"

415 AO_THUMB_GO_ARM

416 AO_BR_ALIGN

418 " ldrex %0, [%4]\n"

419 " and %1, %0, %3\n"

421 " strex %0, %1, [%4]\n"

422 " teq %0, #0\n"

423 " bne 1b\n"

426 : "r" (value), "r" (p)

428}

◆ AO_char_fetch_and_add()

| AO_INLINE unsigned char AO_char_fetch_and_add | ( | volatile unsigned char * | p, |

| unsigned char | incr | ||

| ) |

Definition at line 478 of file gcc/arm.h.

479 {

481 int flag;

482

483 __asm__ __volatile__("@AO_char_fetch_and_add\n"

484 AO_THUMB_GO_ARM

485 AO_BR_ALIGN

487 " ldrexb %0, [%5]\n"

488 " add %2, %0, %4\n"

490 " strexb %1, %2, [%5]\n"

491 " teq %1, #0\n"

492 " bne 1b\n"

495 : "r" ((unsigned)incr), "r" (p)

498 }

◆ AO_compare_and_swap()

Definition at line 529 of file gcc/arm.h.

530 {

532

533 __asm__ __volatile__("@AO_compare_and_swap\n"

534 AO_THUMB_GO_ARM

535 AO_BR_ALIGN

536 "1: mov %0, #2\n" /* store a flag */

538 " ldrex %1, [%3]\n" /* get original */

539 " teq %1, %4\n" /* see if match */

541# ifdef __thumb2__

542 /* TODO: Eliminate warning: it blocks containing wide Thumb */

543 /* instructions are deprecated in ARMv8. */

544 " it eq\n"

545# endif

546 " strexeq %0, %5, [%3]\n" /* store new one if matched */

547 " teq %0, #1\n"

548 " beq 1b\n" /* if update failed, repeat */

551 : "r"(addr), "r"(old_val), "r"(new_val)

554 }

◆ AO_double_compare_and_swap()

| AO_INLINE int AO_double_compare_and_swap | ( | volatile AO_double_t * | addr, |

| AO_double_t | old_val, | ||

| AO_double_t | new_val | ||

| ) |

Definition at line 632 of file gcc/arm.h.

634 {

637

638 do {

639 /* AO_THUMB_GO_ARM is empty. */

640 __asm__ __volatile__("@AO_double_compare_and_swap\n"

642 " ldrexd %0, %H0, [%1]\n" /* get original to r1 & r2 */

644 : "r"(addr)

645 /* : no clobber */);

647 break;

648 __asm__ __volatile__(

650 " strexd %0, %3, %H3, [%2]\n" /* store new one if matched */

653 : "cc");

656 }

◆ AO_double_load()

| AO_INLINE AO_double_t AO_double_load | ( | const volatile AO_double_t * | addr | ) |

Definition at line 596 of file gcc/arm.h.

597 {

599

600 /* AO_THUMB_GO_ARM is empty. */

601 __asm__ __volatile__("@AO_double_load\n"

603 " ldrexd %0, %H0, [%1]"

605 : "r" (addr)

606 /* : no clobber */);

608 }

Definition: generic_pthread.h:373

◆ AO_double_store()

| AO_INLINE void AO_double_store | ( | volatile AO_double_t * | addr, |

| AO_double_t | new_val | ||

| ) |

Definition at line 612 of file gcc/arm.h.

613 {

614 AO_double_t old_val;

615 int status;

616

617 do {

618 /* AO_THUMB_GO_ARM is empty. */

619 __asm__ __volatile__("@AO_double_store\n"

621 " ldrexd %0, %H0, [%3]\n"

623 " strexd %1, %4, %H4, [%3]"

626 : "cc");

628 }

◆ AO_fetch_and_add()

Definition at line 338 of file gcc/arm.h.

339{

341 int flag;

342

343 __asm__ __volatile__("@AO_fetch_and_add\n"

344 AO_THUMB_GO_ARM

345 AO_BR_ALIGN

347 " ldrex %0, [%5]\n" /* get original */

348 " add %2, %0, %4\n" /* sum up in incr */

350 " strex %1, %2, [%5]\n" /* store them */

351 " teq %1, #0\n"

352 " bne 1b\n"

355 : "r"(incr), "r"(p) /* 4..5 */

358}

◆ AO_fetch_and_add1()

Definition at line 362 of file gcc/arm.h.

363{

365 int flag;

366

367 __asm__ __volatile__("@AO_fetch_and_add1\n"

368 AO_THUMB_GO_ARM

369 AO_BR_ALIGN

371 " ldrex %0, [%4]\n" /* get original */

372 " add %1, %0, #1\n" /* increment */

374 " strex %2, %1, [%4]\n" /* store them */

375 " teq %2, #0\n"

376 " bne 1b\n"

379 : "r"(p)

382}

◆ AO_fetch_and_sub1()

Definition at line 386 of file gcc/arm.h.

387{

389 int flag;

390

391 __asm__ __volatile__("@AO_fetch_and_sub1\n"

392 AO_THUMB_GO_ARM

393 AO_BR_ALIGN

395 " ldrex %0, [%4]\n" /* get original */

396 " sub %1, %0, #1\n" /* decrement */

398 " strex %2, %1, [%4]\n" /* store them */

399 " teq %2, #0\n"

400 " bne 1b\n"

403 : "r"(p)

406}

◆ AO_fetch_compare_and_swap()

Definition at line 559 of file gcc/arm.h.

560{

561 AO_t fetched_val;

562 int flag;

563

564 __asm__ __volatile__("@AO_fetch_compare_and_swap\n"

565 AO_THUMB_GO_ARM

566 AO_BR_ALIGN

567 "1: mov %0, #2\n" /* store a flag */

569 " ldrex %1, [%3]\n" /* get original */

570 " teq %1, %4\n" /* see if match */

572# ifdef __thumb2__

573 " it eq\n"

574# endif

575 " strexeq %0, %5, [%3]\n" /* store new one if matched */

576 " teq %0, #1\n"

577 " beq 1b\n" /* if update failed, repeat */

579 : "=&r"(flag), "=&r"(fetched_val), "+m"(*addr)

580 : "r"(addr), "r"(old_val), "r"(new_val)

582 return fetched_val;

583}

◆ AO_nop_full()

| AO_INLINE void AO_nop_full | ( | void | ) |

◆ AO_nop_write()

| AO_INLINE void AO_nop_write | ( | void | ) |

Definition at line 105 of file gcc/arm.h.

106 {

107 /* AO_THUMB_GO_ARM is empty. */

108 /* This will target the system domain and thus be overly */

109 /* conservative as the CPUs (even in case of big.LITTLE SoC) will */

110 /* occupy the inner shareable domain. */

111 /* The plain variant (dmb st) is theoretically slower, and should */

112 /* not be needed. That said, with limited experimentation, a CPU */

113 /* implementation for which it actually matters has not been found */

114 /* yet, though they should already exist. */

115 /* Anyway, note that the "st" and "ishst" barriers are actually */

116 /* quite weak and, as the libatomic_ops documentation states, */

117 /* usually not what you really want. */

118 __asm__ __volatile__("dmb ishst" : : : "memory");

119 }

◆ AO_or()

Definition at line 432 of file gcc/arm.h.

433{

435

436 __asm__ __volatile__("@AO_or\n"

437 AO_THUMB_GO_ARM

438 AO_BR_ALIGN

440 " ldrex %0, [%4]\n"

441 " orr %1, %0, %3\n"

443 " strex %0, %1, [%4]\n"

444 " teq %0, #0\n"

445 " bne 1b\n"

448 : "r" (value), "r" (p)

450}

◆ AO_short_fetch_and_add()

| AO_INLINE unsigned short AO_short_fetch_and_add | ( | volatile unsigned short * | p, |

| unsigned short | incr | ||

| ) |

Definition at line 502 of file gcc/arm.h.

503 {

505 int flag;

506

507 __asm__ __volatile__("@AO_short_fetch_and_add\n"

508 AO_THUMB_GO_ARM

509 AO_BR_ALIGN

511 " ldrexh %0, [%5]\n"

512 " add %2, %0, %4\n"

514 " strexh %1, %2, [%5]\n"

515 " teq %1, #0\n"

516 " bne 1b\n"

519 : "r" ((unsigned)incr), "r" (p)

522 }

◆ AO_test_and_set()

| AO_INLINE AO_TS_VAL_t AO_test_and_set | ( | volatile AO_TS_t * | addr | ) |

Definition at line 314 of file gcc/arm.h.

315 {

316 AO_TS_VAL_t oldval;

317 int flag;

318

319 __asm__ __volatile__("@AO_test_and_set\n"

320 AO_THUMB_GO_ARM

321 AO_BR_ALIGN

323 " ldrex %0, [%3]\n"

325 " strex %1, %4, [%3]\n"

326 " teq %1, #0\n"

327 " bne 1b\n"

329 : "=&r"(oldval), "=&r"(flag), "+m"(*addr)

330 : "r"(addr), "r"(1)

332 return oldval;

333 }

◆ AO_xor()

Definition at line 454 of file gcc/arm.h.

455{

457

458 __asm__ __volatile__("@AO_xor\n"

459 AO_THUMB_GO_ARM

460 AO_BR_ALIGN

462 " ldrex %0, [%4]\n"

463 " eor %1, %0, %3\n"

465 " strex %0, %1, [%4]\n"

466 " teq %0, #0\n"

467 " bne 1b\n"

470 : "r" (value), "r" (p)

472}