# Performance Analysis and Modeling of Task-Based Runtimes

A Dissertation Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Blake Andrew Haugen May 2016 © by Blake Andrew Haugen, 2016 All Rights Reserved. This dissertation is dedicated to my family: My wife, Rebekah, for her love and support, My parents, John and Marsha, who instilled a lifelong love of learning, and My brother, Mark, for bringing humor to every situation.

# Acknowledgements

I would like to thank my advisor, Dr. Jack Dongarra, for his patience and support throughout my time at the University of Tennessee. He and the ICL team made my graduate studies a period of incredible learning including many memories that will last a lifetime.

Thank you to Dr. Chad Steed, Dr. Vasilios Alexiades, and Dr. Gregory Peterson for serving on my doctoral committee and providing feedback on my dissertation and research.

I will be forever grateful to my colleagues and mentors at the ICL for their patience and guidance throughout my time here. I specifically would like to thank Dr. Jakub Kurzak, Dr. Piotr Luszczek, Dr. Asim YarKhan, Dr. Mark Gates, Dr. Anthony Danalis, Dr. Hartwig Anzt, Dr. Ichitaro Yamazaki, and Dr. George Bosilca for the many conversations that have profoundly challenged me and shaped my research.

# Abstract

The shift toward multicore processors has transformed the software and hardware landscape in the last decade. As a result, software developers must adopt parallelism in order to efficiently make use of multicore CPUs. Task-based scheduling has emerged as one method to reduce the complexity of parallel computing. Although task-based scheduling has been around for many years, the inclusion of task dependencies in OpenMP 4.0 suggests the paradigm will be around for the foreseeable future.

While task-based schedulers simplify the process of parallel software development, they can obfuscate the performance characteristics of the execution of an algorithm. Additionally, they can create a challenge for users to analyze the performance of their software and tune algorithmic parameters accordingly.

We will present the basic principles of task-based runtimes as well as two new tools developed to assist engineers developing these runtimes and users employing them to parallelize their workloads. The first is a tool allowing users to simulate the execution of their algorithm. The second is an extension to the common execution trace which includes information about task dependencies.

# **Table of Contents**

| 1                             | Introduction |                      |                                             | 1         |

|-------------------------------|--------------|----------------------|---------------------------------------------|-----------|

|                               | 1.1          | Motiva               | ation                                       | 1         |

|                               | 1.2          | .2 Introduction      |                                             | 2         |

|                               | 1.3          | Thesis               | Statement and Original Contributions        | 3         |

|                               | 1.4          | Outlin               | e of the Dissertation                       | 3         |

| 2                             | Bac          | kgrou                | nd                                          | 5         |

|                               | 2.1          | Hardw                | vare Landscape                              | 5         |

|                               |              | 2.1.1                | Multicore CPUs                              | 6         |

|                               |              | 2.1.2                | SMP and NUMA                                | 8         |

|                               |              | 2.1.3                | Dynamic Frequency Scaling and Power Capping | 9         |

|                               |              | 2.1.4                | Accelerators and Hybrid Computing           | 10        |

|                               | 2.2          | 2 Software Landscape |                                             | 12        |

|                               |              | 2.2.1                | Task-Based Runtimes                         | 12        |

|                               | 2.3          | Tile-B               | ased Linear Algebra                         | 17        |

| 3                             | Wo           | rkload               | Simulation                                  | <b>23</b> |

|                               | 3.1          | Relate               | ed Work                                     | 23        |

| 3.2 Discrete Event Simulation |              | te Event Simulation  | 26                                          |           |

|                               |              | 3.2.1                | Simulation Methodology                      | 26        |

|                               |              | 3.2.2                | Tracing                                     | 28        |

|                               |              | 3.2.3                | Model of Kernel Executed inside a Task      | 29        |

|    |        | .2.4 Task Execution Queue           | 39         |  |

|----|--------|-------------------------------------|------------|--|

|    |        | .2.5 Simulation Task Function       | 39         |  |

|    |        | .2.6 Scheduling Race Condition      | 40         |  |

|    | 3.3    | pin Simulations                     | 43         |  |

| 4  | Sim    | ation Results and Applications 4    | 15         |  |

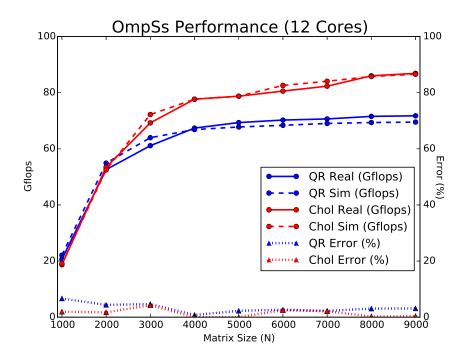

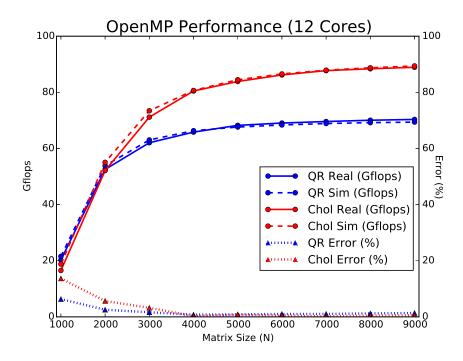

|    | 4.1    | Comparison of Schedulers            | 47         |  |

|    | 4.2    | imulation Scalability               | 50         |  |

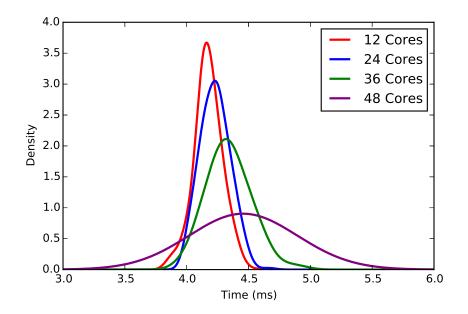

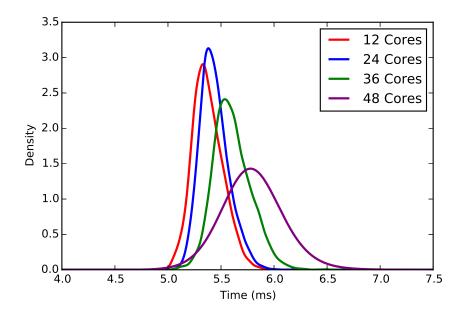

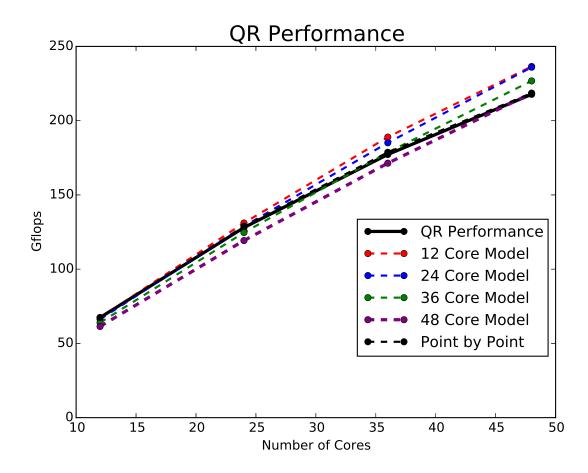

|    |        | .2.1 Varying Core Counts            | 50         |  |

|    |        | .2.2 Varying Task Granularity       | 58         |  |

|    | 4.3    | U Simulation                        | 62         |  |

|    | 4.4    | ntel Xeon Phi Cholesky Simulation   | <u>5</u> 9 |  |

|    | 4.5    | Reverse Trace Performance Modeling  | 78         |  |

|    | 4.6    | Kastors SparseLU Simulation         | 31         |  |

|    | 4.7    | Conclusions                         | 33         |  |

| 5  | Tra    | Visualization 8                     | 35         |  |

|    | 5.1    | ntroduction                         | 35         |  |

|    |        | .1.1 DAG                            | 86         |  |

|    |        | .1.2 Trace                          | 87         |  |

|    | 5.2    | Visualization Design                | 39         |  |

|    |        | .2.1 Implementation                 | 93         |  |

|    | 5.3    | Applications                        | 94         |  |

|    | 5.4    | Trace Visual Analytics System    10 | )0         |  |

| 6  | Cor    | lusions 10                          | )4         |  |

|    | 6.1    | uture Work                          | )6         |  |

| Bi | ibliog | aphy 10                             | )7         |  |

| V  | Vita   |                                     |            |  |

# List of Tables

| 3.1  | DGEMM Cache Scenarios                                 | 33 |

|------|-------------------------------------------------------|----|

| 4.1  | Floating Point Operations                             | 46 |

| 4.2  | DGEQRT task descriptive statistics (25 Data Points)   | 53 |

| 4.3  | DGEQRT t-test p-values                                | 53 |

| 4.4  | DORMQR task descriptive statistics (300 Data Points)  | 54 |

| 4.5  | DORMQR KS test p-values                               | 54 |

| 4.6  | DTSQRT task descriptive statistics (300 Data Points)  | 55 |

| 4.7  | DTSQRT KS test p-values                               | 55 |

| 4.8  | DTSMQR task descriptive statistics (4900 Data Points) | 56 |

| 4.9  | DTSMQR KS test p-values                               | 56 |

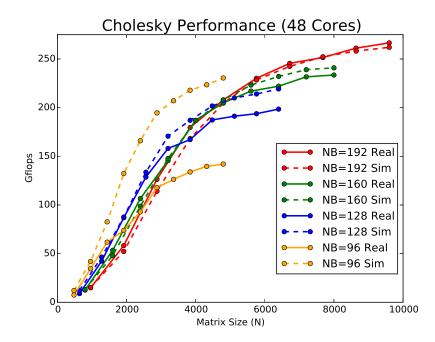

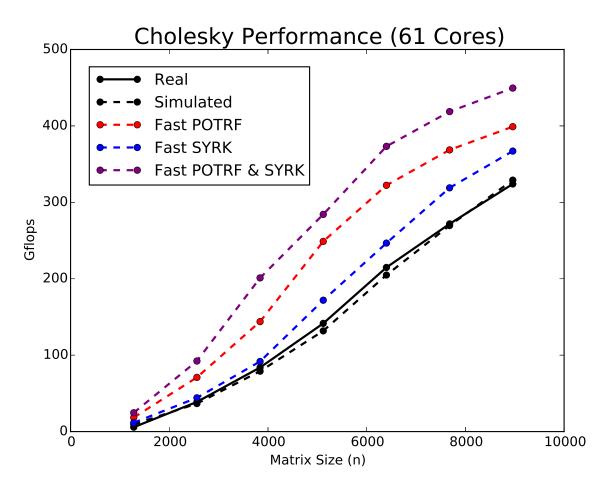

| 4.10 | Cholesky Task Flop Counts                             | 70 |

| 4.11 | Cholesky Task Performance (Intel Xeon Phi)            | 70 |

| 4.12 | Cholesky Task Performance (Intel Haswell)             | 72 |

| 4.13 | Improved DSYRK & DPOTRF Kernel Models                 | 73 |

# List of Figures

| 2.1 | CPU DB Processor Clock Rate           | 6  |

|-----|---------------------------------------|----|

| 2.2 | CPU DB Number of Cores                | 7  |

| 2.3 | Top 500 Total Cores                   | 8  |

| 2.4 | Tile Layout                           | 19 |

| 2.5 | Pseudocode for Tile QR Factorization  | 21 |

| 2.6 | OpenMP Cholesky Implementation        | 22 |

| 3.1 | DGEMM Serial Benchmark                | 35 |

| 3.2 | DGEMM Serial Benchmark                | 35 |

| 3.3 | DGEMM NUMA Benchmark                  | 36 |

| 3.4 | DGEMM NUMA Benchmark                  | 36 |

| 3.5 | DGEMM Threaded Benchmark              | 37 |

| 3.6 | DGEMM Threaded Benchmark              | 37 |

| 3.7 | Simulation Race Condition             | 42 |

| 3.8 | Simulation Race Condition Small Error | 42 |

| 3.9 | Simulation Race Condition Large Error | 42 |

| 4.1 | QUARK Simulation Results              | 48 |

| 4.2 | StarPU Simulation Results             | 48 |

| 4.3 | OmpSs Simulation Results              | 49 |

| 4.4 | OpenMP Simulation Results             | 49 |

| 4.5 | DGEQRT KDE                            | 53 |

| 4.6  | DORMQR KDE                                                    | 54 |

|------|---------------------------------------------------------------|----|

| 4.7  | DTSQRT KDE                                                    | 55 |

| 4.8  | DTSMQR KDE                                                    | 56 |

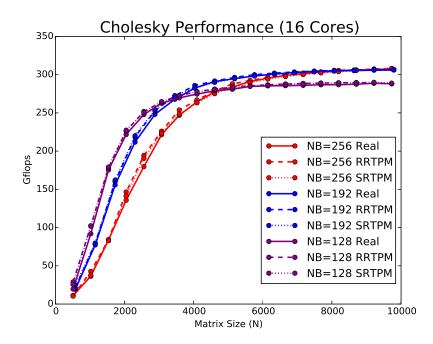

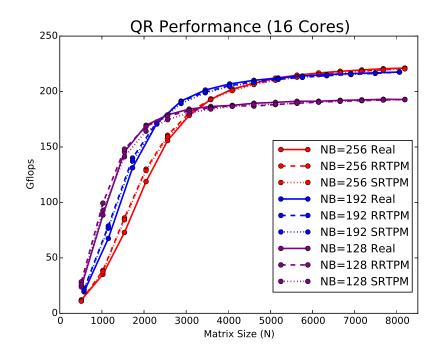

| 4.9  | QR Simulation Scalability                                     | 57 |

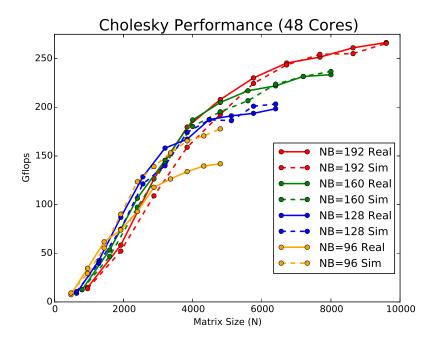

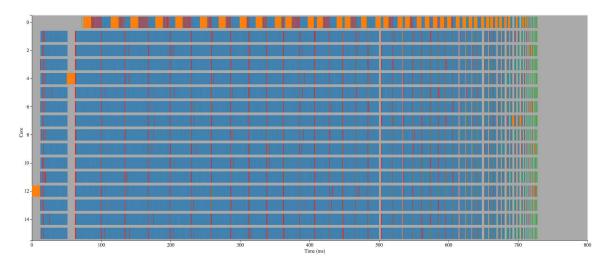

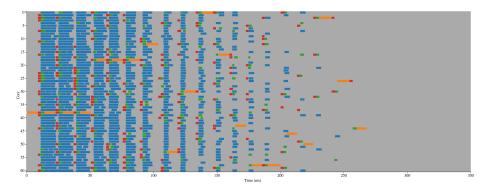

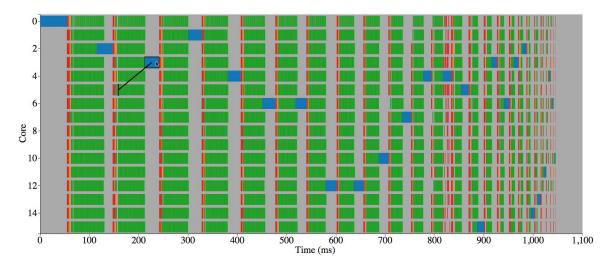

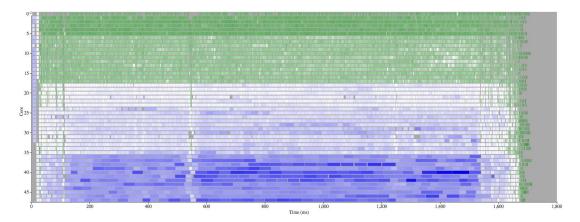

| 4.10 | Cholesky 48 Core Discrete Event Simulation                    | 60 |

| 4.11 | Cholesky 48 Core Spin Simulation                              | 60 |

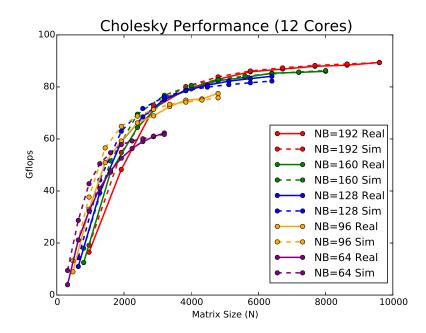

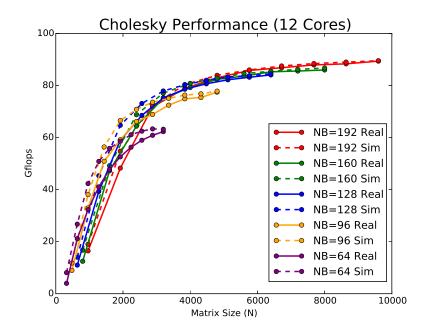

| 4.12 | Cholesky 12 Core Simulation                                   | 61 |

| 4.13 | Cholesky 12 Core Spin Simulation                              | 61 |

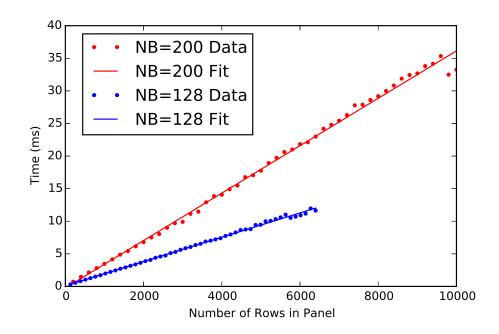

| 4.14 | LU Panel Timing                                               | 65 |

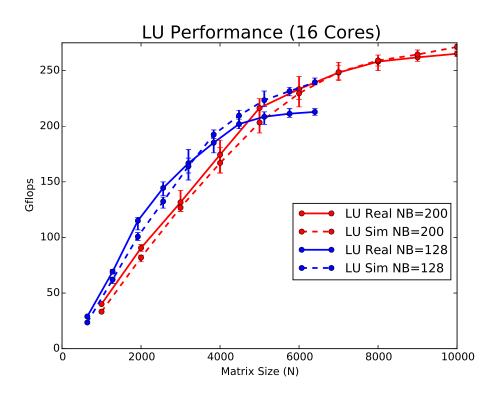

| 4.15 | LU Simulation                                                 | 65 |

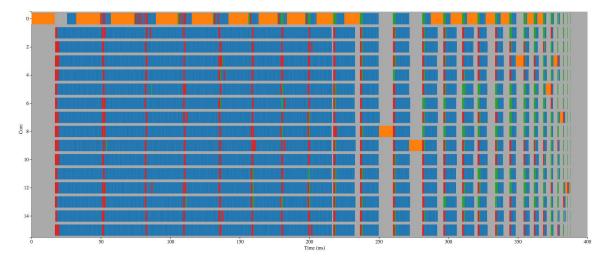

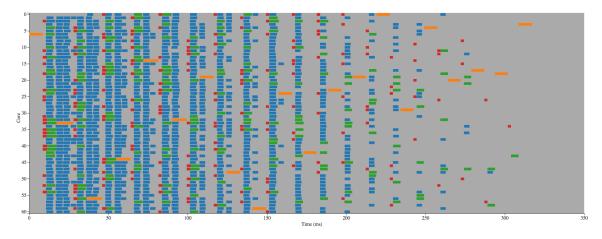

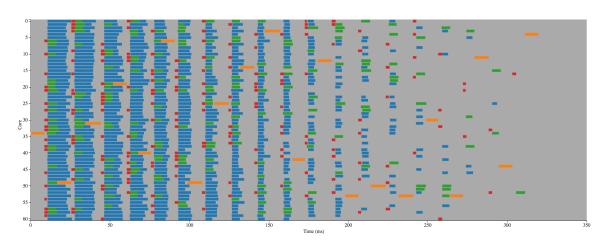

| 4.16 | Real LU Factorization N=5000 NB=200                           | 66 |

| 4.17 | Simulated LU Factorization N=5000 NB=200                      | 66 |

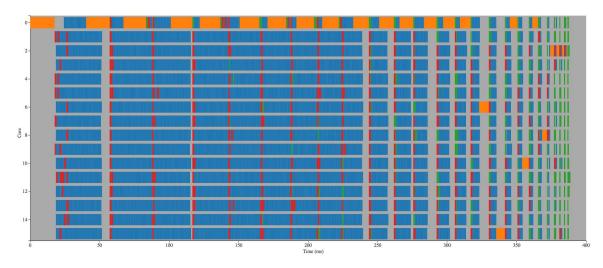

| 4.18 | Real LU Factorization N=6400 NB=128                           | 67 |

| 4.19 | Simulated LU Factorization N=6400 NB=200                      | 67 |

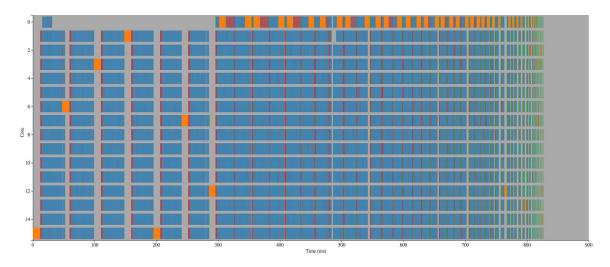

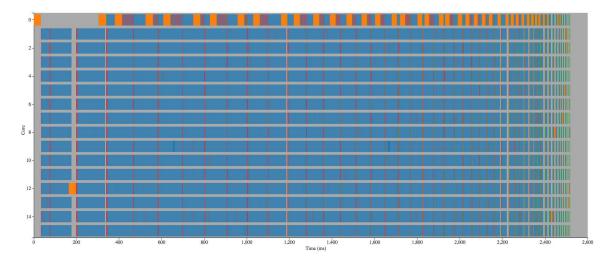

| 4.20 | Real LU Factorization N=10000 NB=200                          | 68 |

| 4.21 | Simulated LU Factorization N=10000 NB=200                     | 68 |

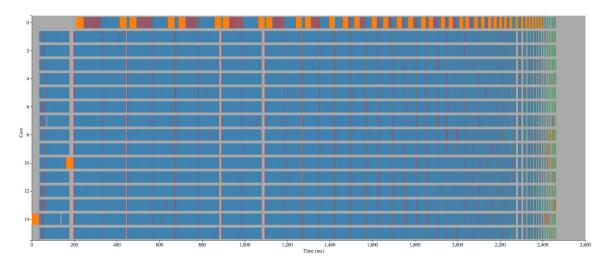

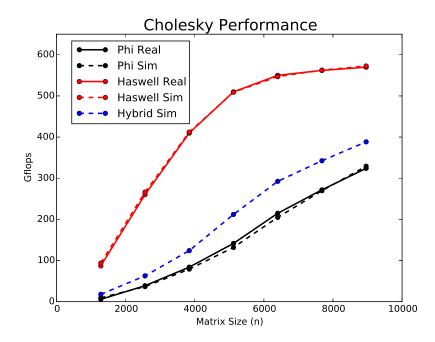

| 4.22 | Simulated Cholesky Factorization (Accelerated Tasks)          | 74 |

| 4.23 | Real Cholesky Factorization                                   | 75 |

| 4.24 | Simulated Cholesky Factorization                              | 75 |

| 4.25 | Simulated Cholesky Factorization (Accelerated DSRYK)          | 76 |

| 4.26 | Simulated Cholesky Factorization (Accelerated DPOTRF)         | 76 |

| 4.27 | Simulated Cholesky Factorization (Accelerated DPOTRF & DSYRK) | 76 |

| 4.28 | Simulated Intel Hybrid Architecture                           | 77 |

| 4.29 | Cholesky Reverse Trace Performance Modeling                   | 80 |

| 4.30 | QR Reverse Trace Performance Modeling                         | 80 |

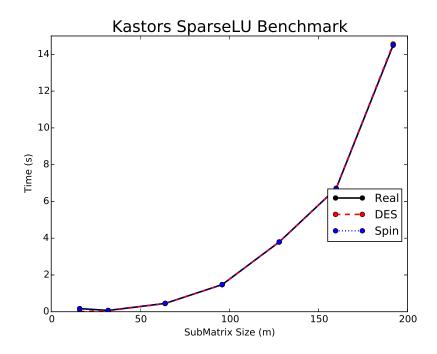

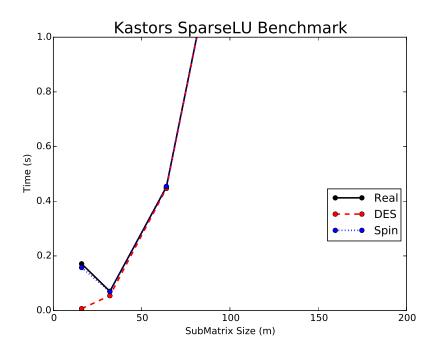

| 4.31 | SparseLU Simulation                                           | 82 |

| 4.32 | SparseLU Simulation                                           | 82 |

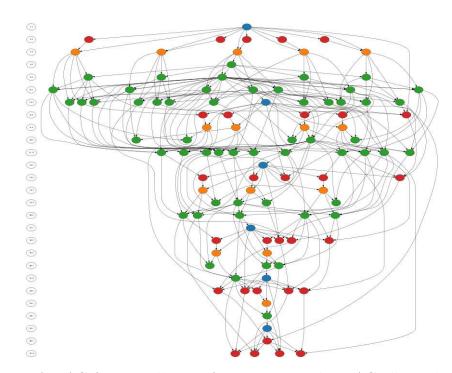

| 5.1  | Example QR DAG                                                | 87 |

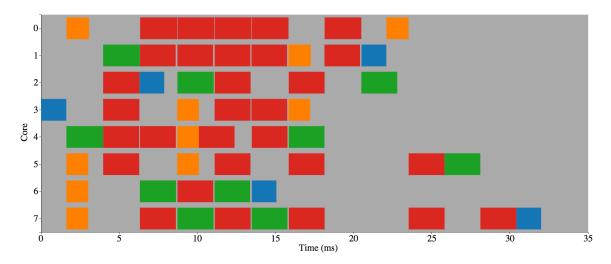

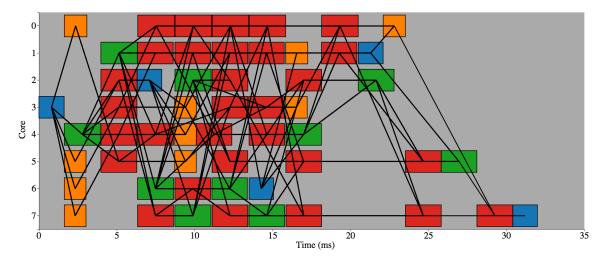

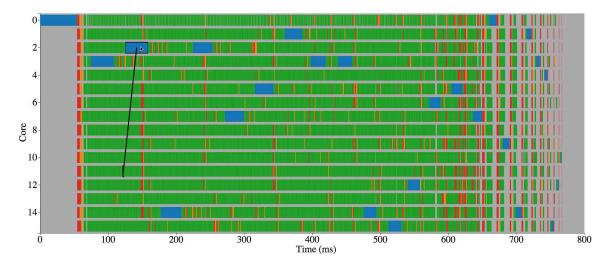

| 5.2  | Example QR Trace              | 88  |

|------|-------------------------------|-----|

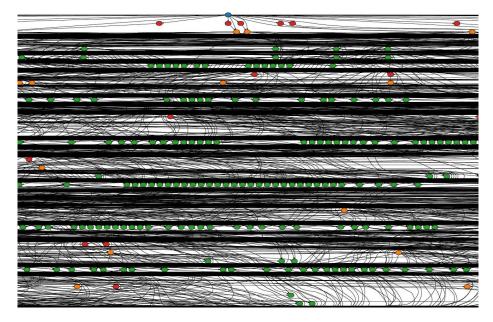

| 5.3  | Complete QR Trace with DAG    | 90  |

| 5.4  | Interactive QR Trace with DAG | 91  |

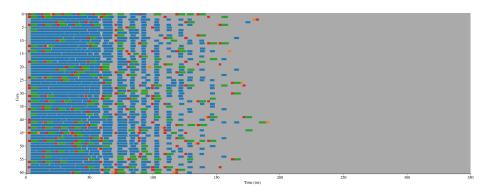

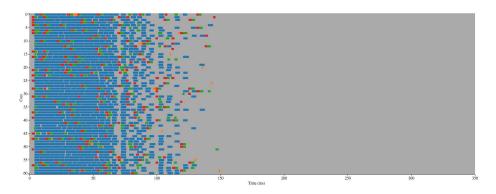

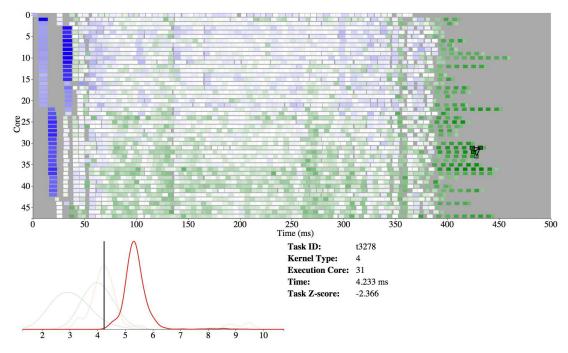

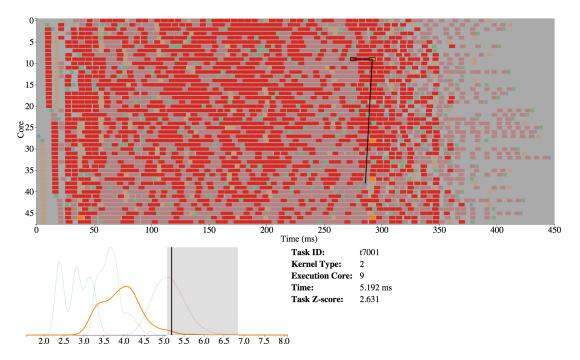

| 5.5  | LU Trace without Priorities   | 95  |

| 5.6  | Large LU DAG                  | 97  |

| 5.7  | Small LU DAG                  | 98  |

| 5.8  | LU Trace with Priorities      | 98  |

| 5.9  | NUMA Performance Issue        | 99  |

| 5.10 | Memory Analysis Trace         | 101 |

| 5.11 | Trace Filtering               | 101 |

# Chapter 1

# Introduction

### 1.1 Motivation

In the last decade the microchip industry has shifted to a multicore paradigm and consequently altered the path of software development. Until this time period, developers could expect their software to see performance improvements with each new generation of computing architecture because the clock frequency of the new chip would boost the performance. During this era, modifications to software were not necessary to increase performance. The frequency of new microprocessors stabilized while the number of cores began to increase. Developers now had to modify their software to make performance gains on new hardware [50]. Unfortunately, adding parallelism to software is often a non-trivial task.

A developer can develop parallel applications using primitive, low-level APIs such as POSIX threads (Pthreads) in a shared memory context or the Message Passing Interface (MPI) standard for distributed memory systems. While effective, these tools generally require expert level knowledge of parallel programming and their application.

A number of higher level parallel programming APIs have emerged in an effort to simplify the process of developing high performance parallel software. One of the programming models that has emerged is a task-based paradigm in which the developer defines his/her computation as a series of tasks executed in parallel by a scheduler at runtime. While this model provides another layer of abstraction to simplify the development process, it also obscures many of the fine-grained details necessary to obtain optimal or near optimal performance. This work presents two new tools designed to give developers a greater understanding of these task-based schedulers.

### **1.2** Introduction

Task-based runtimes simplify the development process by inferring and respecting data dependencies based on developer defined data hazards. In order to use a task-based scheduler, developers must break their workloads into tasks and define the input and output parameters of each task. The scheduler then uses the order of these tasks and their input and output parameters to generate a Directed Acyclic Graph (DAG) of tasks which can be used to schedule the tasks in parallel while respecting all data dependencies. Chapter 2 will give a more extensive introduction to this programming model.

Many of the traditional linear algebra algorithms can be defined as a series of tasks perfectly suited for these task-based schedulers. The tile-based formulation of three common matrix factorizations (Cholesky, LU, and QR) will provide example applications for the remainder of this dissertation. These factorizations and their tile-based implementations will be presented in greater detail in Chapter 2.

The first tool is a simulation utility which can be used to provide insights that guide developers in the process of tuning their task-based applications and the second is an extension to the common execution trace visualization.

### **1.3** Thesis Statement and Original Contributions

The primary goal of this dissertation is to investigate the simulation of task-based runtimes in the context of multicore shared memory architectures. The issues of portability across schedulers and hardware, the accuracy of the performance predictions, and the usefulness to developers are addressed in this document.

The three primary contributions of this dissertation are as follows:

- A novel simulation framework for task-based runtimes. The framework is portable to many task-based schedulers and architectures while providing accurate performance predictions.

- An extension of task benchmarking and timing to multicore machines including extensions for NUMA architectures.

- A novel visualization extension that provides an interactive tool to explore trace and DAG visualizations simultaneously.

### **1.4** Outline of the Dissertation

This dissertation is organized as follows:

- Chapter 2 introduces task-based scheduling and several of the utilities that employ this programming paradigm. Tile-based linear algebra will also be presented in order to provide details about many of the applications which are analyzed throughout this document.

- Chapter 3 describes the simulation framework.

- Chapter 4 presents several applications and a wide variety of performance results for the simulator.

- Chapter 5 presents a novel trace visualization utility designed with extensions for task-based applications.

- Chapter 6 concludes the dissertation and discusses possible future extensions to the work presented here.

# Chapter 2

# Background

Portions of this chapter are drawn from the following publications:

- Haugen, Blake, Jakub Kurzak, Asim YarKhan, Piotr Luszczek, and Jack Dongarra. "Parallel Simulation of Superscalar Scheduling." In the 43rd International Conference on Parallel Processing (ICPP), 2014, pp. 121-130. IEEE, 2014.

- Haugen, Blake, Stephen Richmond, Jakub Kurzak, Chad A. Steed, and Jack Dongarra. "Visualizing Execution Traces with Task Dependencies." In Proceedings of the 2nd Workshop on Visual Performance Analysis, p. 2. ACM, 2015.

I was responsible for the design and implementation of the software corresponding to each of these publications. In addition, I served as the primary author.

### 2.1 Hardware Landscape

Early generations of computing hardware were relatively simple and homogeneous compared with todays systems. In order to deal with power limitations and the desire for ever-increasing application performance, the high performance computing industry has adopted an increasingly diverse set of complex architectures and technologies to provide the best performance possible.

#### 2.1.1 Multicore CPUs

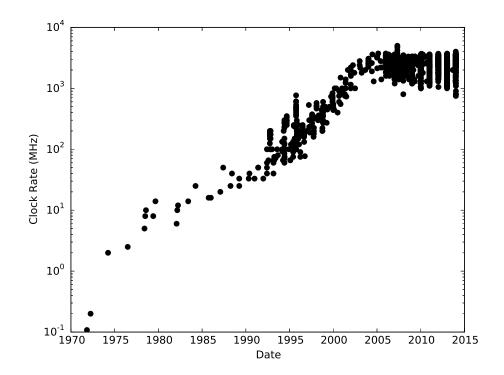

Figure 2.1: The CPU clock rate stagnates around 2005.

The last decade has ushered in a dramatic shift in computer architecture with the introduction and market saturation of multicore processors. Multicore processors have even spread from traditional high end computing platforms to mobile devices such as tablets and smart phones. Prior to the multicore shift, software developers could expect their applications to see significant performance increases with each new architecture. One of the primary reasons for this increase was the ever-increasing clock rate on each processor entering the market. This trend can be seen in Figure 2.1 based on data from the CPU DB data set [23] provided by researchers at Stanford University. The plot shows this ever-increasing clock rate stops fairly suddenly around 2005. Some of the newer processors even have a slower clock rate than older models.

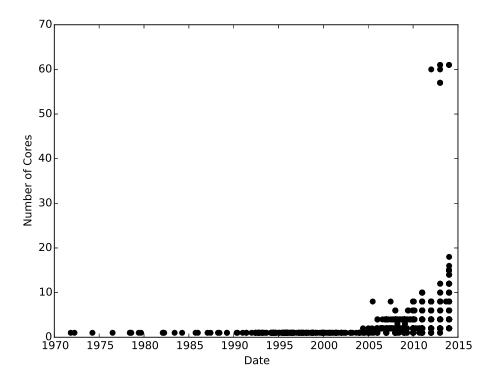

Figure 2.2: The number of cores in a processor begins to increase around 2005.

The CPU DB data set also contains information about the number of cores in each of the processors. This data is plotted in Figure 2.2. Around the same time the clock rate for new processors stagnates, the earliest multicore CPUs begin to emerge. The earliest multicore processors had two cores on the same die but they quickly released chips with many more cores. There are a few data points in the top right corner of Figure 2.2 that are between 57 and 61 cores. These data points correspond to the Intel Xeon Phi manycore architecture (to be discussed in greater depth later).

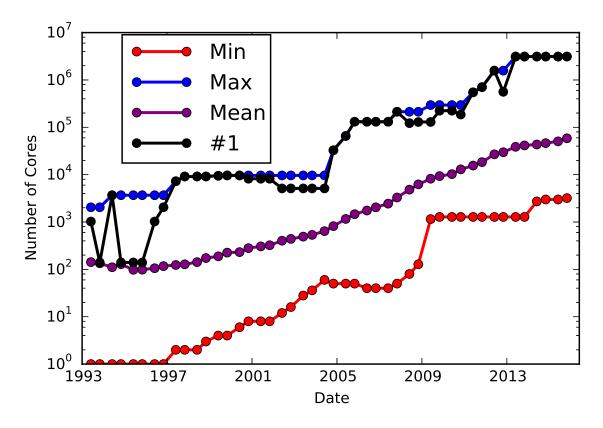

This trend toward an increasing number of cores can also be seen by examining the list of Top 500 supercomputers compiled every 6 months. Figure 2.3 shows a dramatic spike in the number of cores on the top system around 2005.

Perhaps the greatest impact of this multicore shift has been to the software development community. In the past they could run their old software on a new architecture and generally expect drastic performance improvement. In the move to a multicore architecture, however, developers must rewrite their software to make use

Figure 2.3: The number of cores on the Top 500 supercomputer list begins to dramatically accelerate around 2005.

of the parallelism that is available to them. Unfortunately, this is often a non-trivial task requiring a great deal of effort.

#### 2.1.2 SMP and NUMA

Multicore shared memory systems are often broken into two classes which provide different performance characteristics for parallel applications.

The first type of multicore shared memory system is a Symmetric MultiProcessing (SMP) system. An SMP system is made up of multiple processors (cores or chips) connected to a single, shared main memory. This means the main memory is equally accessible by each processor in the system. As a result, it does not matter (assuming the data is not in the cache of another processor) where an application or function is executed because the processors all have the same access to the memory. Most of the

desktops and laptops produced today could be considered SMP systems where each core is a processor and all of the cores share a single main memory.

The other type of multicore shared memory system is a Non-Uniform Memory Access (NUMA) system. A NUMA system also has multiple processors but each processor has access to local memory and non-local memory. The process can access data on any of the NUMA "nodes" but it is faster to access local memory as opposed to non-local memory. This can increase memory throughput for some applications because the processors can each access its own local memory simultaneously. Unfortunately, this architecture can be harder to optimize performance because ideally a developer should execute an application or function on a processor that is "closest" to the memory where the data resides. The developer also has the ability to control where memory is allocated. The most common memory location policy is the "first touch" policy that says the data will be located on the memory closest to the processor that first touches it. The policy for memory placement can also be altered using the numactl utility.

#### 2.1.3 Dynamic Frequency Scaling and Power Capping

One of the primary reasons the clock frequency began to stagnate around 2005 was a problem often called the "power wall." The power a processor consumes is directly related to the frequency of the clock rate. As a result, the ever-increasing clock rate translated to an ever-increasing need for power and the ability to dissipate the heat created with an increase in power.

One of the methods devised to deal with the issue of power is dynamic frequency scaling. These processors have the ability to operate at a variety of clock frequencies determined by the load on the system. The clock rate can be temporarily boosted (consuming more energy) for a short time when the system is under heavy load. Conversely, there is no need to have the system run at the maximum frequency when the system is idle or nearly idle. In this situation the system clock frequency can be reduced and save energy.

Another area of research and development is the concept of power capping where the frequency of the processor can be scaled in such a way that a set power limit is not exceeded. This type of technology can be useful in large scale data centers where power is of great concern. One of the most well-known utilities for power monitoring and control is Intel Running Average Power Limit (RAPL). Developers can use RAPL to get an idea of how much power their CPUs are consuming at any time during the execution of an application. Users can also set a power limit that must be met as long as it is within a safe operating range for the system. The processor will then adjust the performance of the processor in order to stay within that power limit.

It is imperative developers consider technologies like dynamic frequency scaling and power capping when designing and executing their applications. For example, the performance of a section of code may be dramatically affected by the current load on the system or the power capping settings on the machine.

#### 2.1.4 Accelerators and Hybrid Computing

High performance computing has also seen the introduction of accelerators or coprocessors that can be used to accelerate portions of a computational application. NVIDIA originally produced Graphic Processing Units (GPUs) as an extra chip dedicated to rendering graphics. However, these highly parallel architectures were an excellent fit for many applications. The architectures, however, were extremely difficult to use for general purpose computing. As a result, NVIDIA introduced the CUDA architecture and API to make it easier to develop other applications for these architectures.

OpenCL was developed as an open standard for programming accelerators and it is the primary API for programming AMD GPUs. As an open standard, OpenCL can be used to program a wide array of hardware including GPUs, CPUs, and even Field Programmable Gate Arrays (FPGAs).

Intel has blurred the lines between traditional CPUs and accelerators with the introduction of the Intel Xeon Phi (formerly called the Many Integrated Core architecture or MIC). The Xeon Phi is a Manycore architecture that has a large number (61 cores in the most recent model) of x86 cores. Each of the cores can run 4 threads per core and has a 512 bit AVX vector unit. The Xeon Phi was originally designed as a co-processor that can be used to offload heavy computational workloads. However, the next generation of Xeon Phi products (called Knights Landing) will be available as a co-processor or a self-hosted processor. One of the key selling points for the Intel Xeon Phi is the compatibility with the x86 instruction set that makes it relatively simple to port almost any preexisting code base to the new architecture.

Much of the hybrid computing landscape to this point has employed two separate chips in order to create a hybrid machine. This paradigm works in many applications but it also has its drawbacks. The most obvious is the necessity to move data from one device to another because the accelerators typically have their own memory that is separate from the system main memory. Some of this memory transfer can be hidden from the developer but the data transfer can still be a bottleneck in some applications.

Two projects seem to point to the possibility of a more unified hybrid architecture in the future. The first is the AMD Accelerated Processing Unit or APU that combines the traditional CPU cores and GPU cores on the same die. In the embedded field, NVIDIA has released the TK1 and TX1 as part of their Tegra line of processors designed for mobile and embedded applications. The new TX1 includes 4 ARM Cortex-A57 cores, 4 ARM Cortex-A53 cores and a 256 core Maxwell GPU. These two projects suggest that even if the accelerator and CPU unify on the same chip, developers may still be challenged to produce software that efficiently uses the variety of resources available.

### 2.2 Software Landscape

#### 2.2.1 Task-Based Runtimes

Task-based scheduling has emerged as a key strategy to deal with the increasing parallelism in modern high performance computing. In order to apply the task-based computation model, the developer must first break a computational workload into tasks. For some applications, each of the tasks may be independent and can be performed without regard for order. These types of workloads are often described as being embarrassingly parallel. Generally, this class of problems has been relatively easy to solve using a master-worker paradigm.

There are other workloads, however, that may require that tasks be completed in a specific order to ensure the correctness of the computed solution. In the past this problem has often been solved using fork-join parallelism or bulk-synchronous programming. While this programming model does exploit the parallelism of modern computing architectures, it often is not the most efficient method to schedule these tasks. This is particularly true as modern computing architectures have increasing levels of parallelism making global synchronizations more costly. As a result, a new programming model emerged that reduces or eliminates global synchronizations in favor of asynchronous execution.

This model is often referred to as task-based scheduling, a task-based runtime, or task-superscalar execution. The systems that fall under this category tend to have a few characteristics in common. The first and most obvious commonality of these utilities is that the computation must be broken into a number of tasks that must be executed. The second characteristics is a set of dependencies between the task that must be respected in order to ensure the accurate completion of the algorithm. These dependencies are often depicted and represented by a Directed Acyclic Graph (DAG.) In this DAG, each of the nodes in the graph represents one of the tasks in the computational workload and each edge represents a data dependency. In most cases (with the exception PARSEC), this DAG does not need to be explicitly defined by the developer. Rather than define the DAG manually, the developer must label the parameters for each task as one of the following:

- **INPUT** A parameter designated as *INPUT* will be read during the task but will not be modified.

- **INPUT** A parameter designated as *OUTPUT* will be modified or written during the execution of the task.

- **INPUT** and **OUTPUT** These parameters are often referred to as *INOUT* and are used to designate parameters that will be read **and** written to during the execution of the task.

The tasks are then presented to the scheduler in a sequential fashion. Based on the parameter labeling and the order they are presented, the scheduler is able to generate the DAG. The dependencies are classified as one of the following:

- Read after Write (RAW) A RAW dependency implies a task must wait until the previous task has written a piece of data before it can be read by another task.

- Write after Write (WAW) A WAW dependency implies a task must wait until an earlier task has written a piece of data before it can be written again.

- Write after Read (WAR) A WAR dependency implies a task must wait until another task has written a piece of data before it can be read and used.

These dependencies are generally queued on the data objects or pointers and each task must wait until any prior dependency for one of its parameters has been satisfied.

This type of execution is sometimes referred to as task-superscalar because of the similarities to superscalar instruction scheduling in computer architecture. Tomasulo's algorithm [52] allows for an efficient out-of-order execution of instructions in modern computing architectures. In this fashion, tasks may be scheduled in any order as long as there are no data hazards that must be satisfied.

Another hallmark of these task-superscalar schedulers is an execution that is nondeterministic. This means tasks may not be executed in the same order or on the same resources from one execution to the next. This allows the scheduler to make decisions at runtime and makes them less susceptible to unexpected performance issues. For example, if one of the worker threads has completed its allotted work, it may "steal" work from another worker in order to balance the workload across the system.

#### OmpSs

The OmpSs system, developed at the Barcelona Supercomputing Center, dates back to 1994. It was originally targeting grid environments, and was called GridSs [11]. It was later adapted to the IBM Cell B. E. processor under the name CellSs [39], and then to classic multicore processors (x86 and alike) under the name SMPSs [40, 40, 10]. The extension to GPUs (GPUSs) was introduced in 2009 [9]. The project is currently named OmpSs to underline the effort to extend the OpenMP standard with support for superscalar scheduling [25]. Due to the multiplicity of names, the project has also been intermittently referred to as StarSs [42]. The best known variant is the SMPSs multicore implementation, which is a compiler-based system that uses **#pragma** directives to annotate tasks that can be run in parallel and to decorate the data parameters with read/write usage information.

The main thrust in OmpSs is to become part of the OpenMP standard. Therefore, for the most part, OmpSs follows the OpenMP philosophy of offering a set of simple language extensions for quickly parallelizing algorithms. However, OmpSs does lack some of the flexibility of other libraries such as StarPU and QUARK. The project relies on the Mercurium compiler and the runtime environment is maintained by a library called Nanos++.

#### QUARK

QUARK (QUeuing And Runtime for Kernels) was developed at the Innovative Computing Laboratory at the University of Tennessee Knoxville. It was originally developed as the main scheduler for the Parallel Linear Algebra for Scalable Multicore Architectures (PLASMA) library [1]. It has since been released as a standalone project [59] and has been used outside its original design to schedule for a wider variety of scientific codes. In general, QUARK provides a relatively small API but it still allows the user greater flexibility in code development. The library includes a number of features critical to the operation of a numerical software suite, such as error handling extensions and task cancellation capabilities. It also provides the user with the ability to save the execution DAG to visualize the dependences present in a particular algorithm.

QUARK was originally aimed at scheduling for homogeneous multicore systems with shared memory. It has since been used to develop software for systems containing GPUs as well as traditional CPUs [32]. It should be noted that QUARK does not provide any specific interface for accelerator support. It is the responsibility of the developer to ensure data is transferred properly during the execution of the algorithm. It has also been extended to applications in distributed memory environments [58].

#### StarPU

The StarPU system developed at INRIA Bordeaux was first published in 2008 [5, 7, 6]. It is a runtime environment for task scheduling on shared memory architectures with the original motivation of exploring task scheduling in a hybrid CPU/GPU environment.

StarPU provides multiple interfaces for task execution which gives the developer great flexibility in expressing an algorithm. One of the key abstractions of the StarPU library is the codelet. The codelet is a small structure that allows the developer to describe various versions of a particular kernel using a single interface. For example, the developer might want to define a matrix multiplication task for use in his/her algorithm. The user can define a codelet providing a CPU interface as well as a GPU interface allowing StarPU to execute the code on either of the target resources. StarPU uses implicit data dependencies to create a task DAG. It also profiles each task execution and uses historical runtime data to schedule tasks on the appropriate resources in heterogeneous systems, assigning tasks to CPU cores as well as GPU resources. StarPU provides a large set of interfaces and extensive functionality including execution trace, DAG generation, and several scheduling policies.

#### OpenMP

OpenMP [22] has a long history in parallel computing and continues to evolve to suit a growing number of applications. Early OpenMP standards provided compiler directives for loop level parallelism. In these applications the developer could write a simple **for** loop and OpenMP would execute the iterations of the loop in parallel.

OpenMP 3.0 [36] was released in May 2008 and added the first task constructs to the standard. These tasks, however, would not be considered task-superscalar because they largely followed the fork-join model of parallelism. In this model the tasks are generated and executed in parallel while a *taskwait* construct is used to synchronize the tasks.

OpenMP 4.0 [37] was released in July 2013 and extended the task constructs to include task-superscalar concepts. The developer can now specify the input and output dependencies for each task block and the OpenMP scheduler will execute the tasks based on the inferred dependencies. Many in the task-based scheduling community view the inclusion of task-superscalar concepts as validation of the field and suggest it will be an active area of research for years to come. OpenMP 4.0 also included constructs for accelerators and SIMD instructions.

OpenMP 4.5 [38] was released in November 2015 and included one key feature not available in version 4.0. The priority clause has been added to the task construct and can be useful in many applications. The developer can now give each task a priority level. If more than one task is available for execution, the task with higher priority should be executed first. This is a concept often used to give priority to tasks known to be bottlenecks or an important part of the critical path of the application.

OpenMP supports Fortran, C, and C++ and is implemented in many open source and proprietary compilers. Perhaps the two most known implementations of OpenMP are available in GCC and the Intel compiler suite. OpenMP has also received interest from the accelerator community because it is one of the primary programming models which can be used to program the many-core Intel Xeon Phi chips.

#### PARSEC

PARSEC [15] is a dataflow scheduler requiring explicit dependencies from the developer but it provides much greater scalability. The computation is represented in a job description format (JDF) file defining the tasks and dependencies in a compact format. This format allows the runtime to determine dependencies without unrolling the entire DAG. The ability to determine dependencies independently makes the runtime far more scalable. PARSEC provides the underlying scheduling and runtime for a scalable dense linear algebra library called DPLASMA. In contrast with many of the other task-based schedulers, PARSEC focuses on scheduling scalability in a distributed computing environment.

### 2.3 Tile-Based Linear Algebra

Dense linear algebra algorithms provide the basis for many scientific computing problems and remain an area of active research. These algorithms have evolved over time in order maximize performance with each new generation of hardware. Block algorithms were introduced with LAPACK [4] in order to make use of the caches on the newest architectures of the day. Achieving optimal performance for each new architecture would have been a challenging task. Block algorithms, however, simplified this problem by defining a set of Basic Linear Algebra Subroutines (BLAS) that would be the building blocks for the higher level algorithms. Rather than adapting every algorithm to achieve optimal performance, developers could optimize the smaller collection of BLAS routines in order to achieve high performance for each architecture and the linear algebra operations built on top of them would also achieve high performance. There are three classes of operations in the BLAS often referred to as Level 1, Level 2, and Level 3. They refer to vector-vector operations, matrix-vector operations, and matrix-matrix operations respectively. Level 3 BLAS (matrix-matrix) operations are generally preferred because of the data reuse inherent in their algorithms. This data reuse exploits the caches in modern architectures and reduces data movement which generally resulting in higher performance. The Level 1 and Level 2 operations are memory bound and as a result, they generally do not reach optimal performance.

The basic formulation for many of the block algorithms is a two step approach. The first step is often referred to as the panel factorization where a small portion of the matrix is factorized and transformations are accumulated. This factorization is generally memory bound and do not achieve optimal performance. The second portion of the operation is often called the trailing submatrix update. This step applies the transformations from the panel factorization to the remaining portion of the matrix. The update step is generally applied using a Level 3 BLAS operation.

Parallelization of block linear algebra algorithms has often been performed using a fork-join model where the parallelism is generally expressed in the trailing submatrix update. This paradigm, however, struggles to provide the best performance on modern highly parallel architectures because of the costs of synchronization. Tilebased linear algebra algorithms have been developed in order to make better use of multicore resources. Two of the primary reasons these tile-based approaches achieve higher performance are the reduction in global synchronization and the more efficient use of caches.

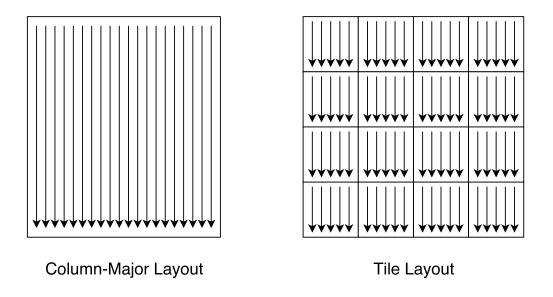

One of the key differences between the two approaches is the way the data is laid out in memory. Previous algorithms required the matrix to be allocated in a single array using column-major or row-major layout as seen on the left in Figure 2.4. For a tile-based approach, however, the matrix is stored by blocks as shown on the right in Figure 2.4.

Figure 2.4: Colmn-Major Layout vs Tile Layout

These tile-based algorithms can be found in the PLASMA library developed at the University of Tennessee as well as the FLAME library from the University of Texas at Austin [28]. Tile-based linear algebra has been extensively studied [24, 29, 33, 2, 17]. The Cholesky, LU, and QR factorizations implemented in PLASMA will provide the basis for many of the experiments presented in this paper.

The tile approach consists of breaking the matrix panel factorization and trailing submatrix update steps into smaller tasks that operate on relatively small  $NB \times NB$ tiles (or submatrices) of consecutive data which are organized into blocks-of-columns. The algorithms can then be restructured as tasks (which are basic linear algebra operations) that act on tiles of the matrix. The data dependencies between these tasks result in a DAG where nodes of the graph represent tasks and edges represent dependences among the tasks.

The execution of the tiled algorithm is performed by asynchronously scheduling the tasks in a way that dependencies are not violated. Optimally, we would like

Algorithm 1 Tile Cholesky Factorization Algorithm

1: for k = 1, 2 to NT do 2:{Cholesky factorization of the tile  $A_{k,k}$ } 3:  $DPOTRF(A_{k,k})$ for i = k + 1 to NT do 4: {Solve  $A_{k,k}X = A_{i,k}$ } 5: $DTRSM(A_{k,k}, A_{i,k})$ 6: {Update  $A_{i,i} \leftarrow A_{i,i} - A_{i,k}A_{i,k}^T$ } 7:  $DSYRK(A_{i,i}, A_{i,k})$ 8: 9: end for 10:for i = k + 2 to NT do for j = k + 1 to i do 11: 12:{Update  $A_{i,j} \leftarrow A_{i,j} - A_{i,k}A_{j,k}$ } 13: $DGEMM(A_{i,j}, A_{i,k}, A_{j,k})$ end for 14:end for 15:16: end for

this asynchronous scheduling to result in an out-of-order superscalar execution where slower tasks are overlapped in time with fast ones, which use cache more effectively. This would be managed by having the slower tasks start early, as soon as their dependencies are satisfied, while some of the parallel tasks (submatrix updates) from the previous iterations still remain to be performed and can be executed in parallel when a core becomes available. The scheduling of tasks is performed by the task-based runtime or scheduler.

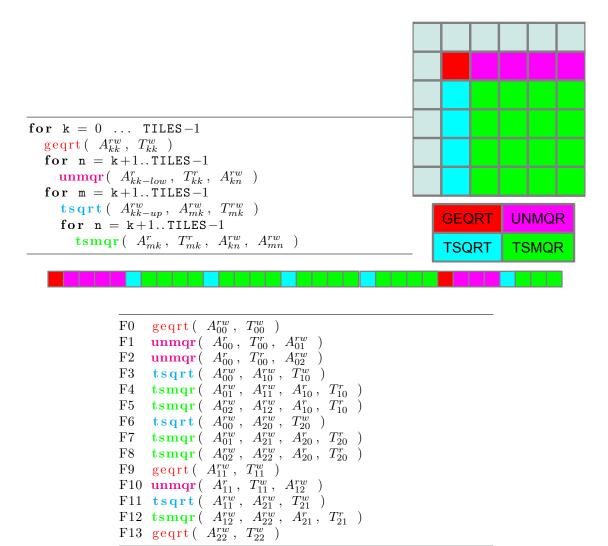

Figure 2.5 presents the loops for the QR factorization in pseudocode and includes decorators for each tile to specify whether the tile will be read, written, or both. These dependencies are then used to infer the DAG and schedule the tasks accordingly.

Each of the tasks and corresponding dependencies must be presented to the scheduler. Each scheduling library provides their own API that is used to annotate the tasks and their dependencies. Some of them, like QUARK and StarPU, have an explicit interface that is used to "insert" tasks. OmpSs and OpenMP, however, provide compiler directives that are used to specify the tasks and their dependencies. The Cholesky algorithm is described in pseudocode Algorithm 1. Figure 2.6 presents the Cholesky algorithm implemented using the OpenMP compiler directives.

Figure 2.5: Pseudocode for the tile QR factorization showing all the tasks as they are sequentially generated. The data references tasks are decorated with their read and/or write status, implying data-hazards while executing the tasks.

```

#pragma omp parallel

#pragma omp master

{

for (k = 0; k < nt; k++) {

#pragma omp task depend(inout:A(k, k)[0:nb*nb])

LAPACKE_dpotrf_work(

LAPACK_COL_MAJOR,

'L', nb, A(k, k), nb);

for (m = k+1; m < nt; m++) {

#pragma omp task depend(in:A(k, k)[0:nb*nb]) \

depend(inout:A(m, k)[0:nb*nb])

cblas_dtrsm(

CblasColMajor,

CblasRight, CblasLower,

CblasTrans, CblasNonUnit,

nb, nb,

1.0, A(k, k), nb,

A(m, k), nb);

for (m = k+1; m < nt; m++) {

#pragma omp task depend(in:A(m, k)[0:nb*nb]) \

depend(inout:A(m, m)[0:nb*nb])

cblas_dsyrk(

CblasColMajor,

CblasLower, CblasNoTrans,

nb, nb,

-1.0, A(m, k), nb,

1.0, A(m, m), nb);

for (n = k+1; n < m; n++) {

#pragma omp task depend(in:A(m, k)[0:nb*nb]) \

depend(in:A(n, k)[0:nb*nb]) `

depend(inout:A(m, n)[0:nb*nb])

cblas_dgemm(

CblasColMajor,

CblasNoTrans, CblasTrans,

nb, nb, nb,

-1.0, A(m, k), nb,

A(n, k), nb,

1.0, A(m, n), nb);

}

}

}

}

```

Figure 2.6: The tile-based Cholesky factorization implemented in OpenMP. Corner cases are ignored to improve clarity.

## Chapter 3

# Workload Simulation

This chapter and Section 4.1 are based on the following publication by Blake Haugen et al.:

Haugen, Blake, Jakub Kurzak, Asim YarKhan, Piotr Luszczek, and Jack Dongarra. "Parallel Simulation of Superscalar Scheduling." In the 43rd International Conference on Parallel Processing (ICPP), 2014, pp. 121-130. IEEE, 2014.

My contributions to this paper include (i) design of the simulation framework, (ii) implementation of simulation software, (iii) collection of experimental data, (iv) analysis of the experimental results, and (v) authorship of the majority of the text.

### 3.1 Related Work

Since the Minimum Multiprocessor Scheduling Problem is NP-complete [35], nearly all optimal scheduling problems in complex environments are NP-complete. This means most scheduling decisions are reached using heuristic algorithms, many of which can be found in the survey article [34]. The combination of complicated hardware configurations and scheduling heuristics make the search space too large and complex for analytical models. As an alternative to most analytical models, developers often resort to empirical and simulation-based models [3, 55].

Simulation is not a new concept to computer scientists, and simulation tools seem to fall into two broad categories. The first is architecture simulation where the goal is to simulate the operation of a processor or system in order to analyze the accuracy of the output or performance characteristics. These simulations often do not focus on parallelism, but rather focus on fine-grain, instruction level simulation. The gem5 [14] and SESC [44] simulators are two examples of this type of simulator. An important aspect of both of these tools is the ability to simulate out of order executions, which are common in modern computer architectures.

At the other end of the spectrum are large scale simulations of parallel computing systems. The grid computing community has been particularly interested in simulation. Grid computing resources may be heterogeneous in nature and dispersed geographically and, for this reason, reproducibility of performance results may vary widely. Each allocation of grid resources may be very different and drastically change the performance of a grid computing job. Simulations have been commonly used to evaluate algorithms in this type of environment where it may not be possible to obtain reproducible results.

The diverse array of computing resources used in grid computing makes scheduling a very challenging problem, and the lack of reproducibility in the performance of each run made simulation a logical choice. Tools like SimGrid [19] and GridSim [18] were designed for these types of simulations. ChicSim [43] was another simulator built on top of a simulation language called Parsec (not the same as the task-based scheduler).

The Optorsim project [13] is another example of a grid computing simulator, and was developed to evaluate the performance of various data duplication algorithms. Data is often duplicated in a grid computing environment in order to deal with the geographic distribution of computing resources. The duplication of data decreases data access times and accelerates job performance. The Optorsim project aimed to simulate the performance of grid computations based on the data replication strategies employed.

The Prometheus project [30] provides utilities to simulate task-based applications on many-core systems. Prometheus currently works with Cilk++ but they hope to extend the framework to other programming models in the future. The first step of the simulations is to extract the DAG for the application. This is currently done by intercepting the the Cilk++ keywords and generating a DAG. The second portion of the simulation is a hardware contention model. The hardware contention model is used to model the length of each task in the DAG based on some sort of performance model. These models can be created from workload measurements, cycle accurate simulation or an analytical performance model. Once the DAG and performance models are in place, the simulation proceeds with any number of scheduling algorithms.

The StarPU project has employed SimGrid to provide simulation capabilities within the scheduler. [48, 49, 47] This simulation, like the StarPU scheduler, has put a great deal of focus on hybrid computing systems where data must be transferred between the host and the device. The authors have studied dense linear algebra and a sparse linear algebra solver. When StarPU scheduler is used, it collects performance information about each of the tasks. This information is stored in an XML file that describes the performance characteristics of the system and the performance of the various tasks when they are performed on the system. The XML configuration serves as an input for the simulation and provides performance models for the various tasks in the application. The simulation employs the StarPU scheduler to keep track of the task dependencies and schedule them accordingly. The tasks, however, are simulated and do not perform actual computational work. The SimGrid library provides a thread API that allows the simulation to take control of all thread scheduling decisions.

# 3.2 Discrete Event Simulation

Discrete Event Simulations (DES) have been used to model problems in a variety of fields from healthcare to manufacturing. A DES is an excellent tool for understanding the performance obtained when scheduling various tasks. In general, each task is considered a single unit that does not change the system while it is occurring. The only changes to the system occur when a new task starts or ends. This simplification allows the simulation to ignore each time slice in a traditional continuous simulation.

In a serial context, a DES is trivial because there is only one event occurring at any given time. Therefore, each event is completely independent and it is not necessary to coordinate across multiple events. In a parallel context, a DES becomes more complicated because the events must properly synchronize before the simulation can continue. While non-trivial, this is still relatively easy to accomplish in the context of Fork-Join parallel applications because each event in the simulation must wait for the other events in order to continue with the simulation. Task-based schedulers, however, depart from the fork-join parallel model and make synchronization in any simulation a challenge.

### 3.2.1 Simulation Methodology

The ultimate goal of the simulator is to simulate a trace of the algorithm's execution with high accuracy. From the simulated trace information can be gained about scheduling decisions, execution time, and ultimately performance.

As a foundational principle, the simulation environment aims to have the scheduler performing the dependence tracking work while the computational work inside the tasks is not performed. In other words, the scheduler keeps track of all data dependences and makes all scheduling decisions as usual, but the tasks no longer contribute useful work toward the completion of the algorithm.

Arguably the most challenging aspect of creating correct simulated traces is the necessity to maintain the correct order of task completion. If each simulated task simply records its information in the trace and exits, it is very likely the task dependences will be satisfied in a different order than the original, which can ultimately cause drastic alterations to the simulated trace. The main reason for this is that the original tasks perform useful computations and take time to do so while also interacting with other resources such as shared caches, the memory system, and the OS. A task that records a small piece of trace information and exits will have very little interaction with the hardware resources.

The simulation generally relies on three crucial elements. The first element is the simulation clock which keeps track of the simulation time. The clock is stored as a double precision floating point number which is of sufficient resolution for the simulated tasks that operate at the microsecond resolution. The simulation library must also keep track of the simulated trace (the second element and the output of relevance to the developer) as well as a queue of tasks that are currently executing (the third element).

There are two primary assumptions that must be true in order to ensure accurate simulations.

• The scheduler overhead is small relative to the tasks being scheduled.

After each task in the workload is completed, the scheduler must perform the necessary bookkeeping and schedule the next task. This time between tasks is often called scheduling overhead. One of the most common problems for this class of schedulers is that it struggles when the length of each task becomes too small. In this case, the scheduler becomes a bottleneck and cannot feed enough work to the processors. Another scheduling issue occurs when the number of processors begins to grow. This is logical because there is generally only one thread doing the scheduling. If there are a large number of cores, it can be difficult for the single threaded scheduler to keep up with the demand for tasks from the workers. These are known problems with many of the task-based schedulers and they often cause increasing error in the simulations as well.

• The scheduler does not behave differently because of the simulation. The simulations often do not run at the speed of the real execution. (The speed of the simulations depends on a complex interaction of the number of simulated cores, the number structure of the DAG corresponding to the workload, and the length of each task. In some cases the simulations are faster and in some cases slower.) If the scheduler makes decisions based on the length of each task it may make different scheduling decisions when it is simulating an application.

Examples of the errors are caused when these assumptions are violated will be presented later.

The novelty of our simulation approach is the complete reliance on the scheduler to provide the facilities to maintain the task dependences and make all scheduling decisions while still being portable across multiple schedulers. In order to create a simulation, the programmer simply replaces each task function with a call to the simulation library. Only a few lines of initialization and cleanup code before and after the execution of the algorithm simulation are needed to perform a simulation. This makes our approach portable since there is no assumption about the underlying algorithm being scheduled or about data-dependence tracking, nor do we require any invasive changes to the existing implementation of tasks. The simulation also allows the user to simulate the behavior of the scheduler independent of the computational platform. Once a problem configuration has been defined, the user can simulate their workloads on another machine regardless of the number or type of processors available.

#### 3.2.2 Tracing

In order to simulate a given trace, it is necessary to have complete control over the generation of the execution trace. Most general purpose tracing utilities and frameworks are designed to create traces based on true (or wall-clock) execution time, but the simulation requires a trace based on the simulated (or virtual) execution time. This lead to the following decision. Rather than attempting to modify an existing trace generation tool, a rudimentary trace generation environment was created allowing the user to log tasks during execution with the simulation (user-specified) time. After the completion of the algorithm, the trace is stored in a CSV file. The CSV format was chosen to simplify the process of analyzing the trace data. Many other trace file formats require libraries to read the data, while many languages already provide utilities for manipulation the CSV. This can be useful for performing statistical or structural analysis of the trace. The trace file can also be used to generate a visual representation of the data such as an SVG (Scalable Vector Graphics) or an interactive visualization like the one presented in Chapter 5.

This trace environment is also available to assist developers in collecting information about the tasks in their workload which can be used to build a statistical model for each of the tasks.

#### 3.2.3 Model of Kernel Executed inside a Task

One of the key factors for performing accurate simulations is the ability to accurately measure and describe the execution time of a kernel. Each of the kernels provides the building block of the simulated trace. If the model of a single kernel is inaccurate, the effects will be compounded as the trace is simulated and the kernel invocation repeats. This can be a source of a sizable error in the simulation.

In order to more realistically simulate the execution of an algorithm, each task's running time is not fixed, but rather is determined by a probabilistic distribution. For example, it is unlikely each DGEMM kernel requires exactly the same time to execute in any given trace. The distribution of these kernel times will vary from application to application, or even between the runs of the same application. The generation of running time of the simulated kernels based on a prescribed distribution adds an element of randomness to the trace, which is essential for the accuracy.

#### Timing Methodology

One of the challenges a developer faces in modeling a kernel is timing each kernel. It initially seems obvious that one could very quickly call each kernel in isolation in order to obtain an estimate of the time required for the completion of that kernel. This will likely give the developer an idea of the execution time of the kernel, but this is unlikely to give results with high accuracy. The developer must be careful to consider where the sub-matrix will be in the cache hierarchy. In the context of a true execution, the kernel may or may not have its data available at the top of the cache hierarchy. To make the task even more challenging, on a NUMA machine it is possible that the data required for the task is stored on non-local memory.

In order to quantify the differences in timing methodology, a series of benchmarks were designed to evaluate the performance of a DGEMM task in a number of different scenarios. The benchmark methodology is largely based on the work of Whaley and Castaldo [57] including new extensions for NUMA architectures.

In order to demonstrate the challenges associated with developing a benchmark that accurate reflects the scenarios presented in a real workload, the double precision general matrix-matrix multiplication (DGEMM) task will be studied in great detail. DGEMM is defined as:

$$C \Leftarrow \alpha A \times B + \beta C$$

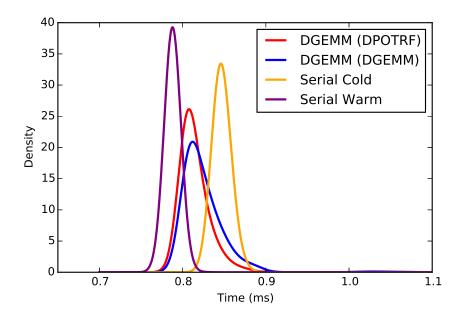

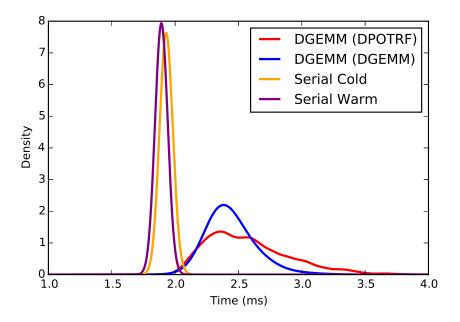

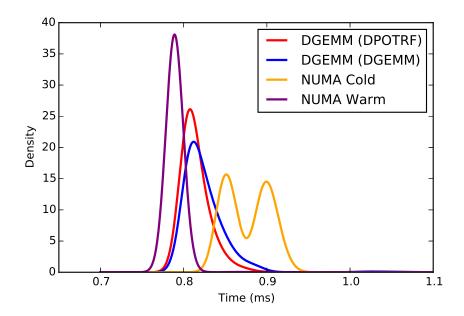

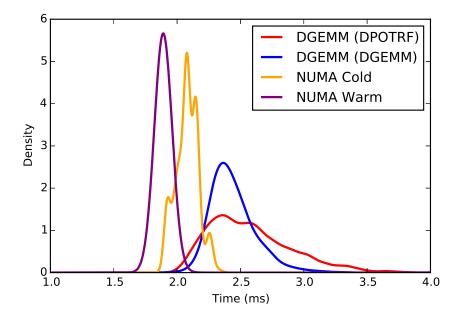

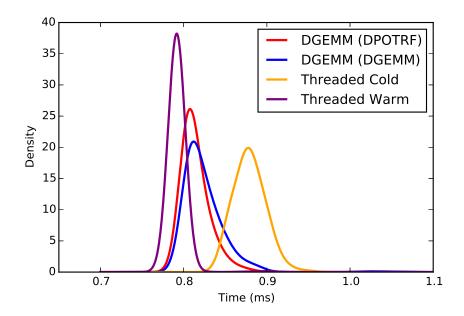

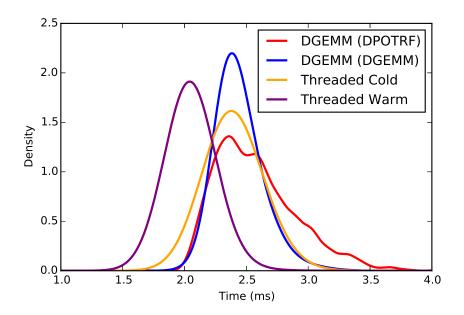

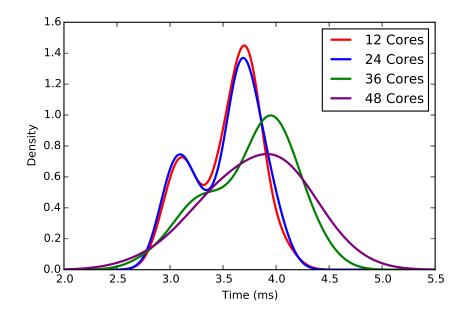

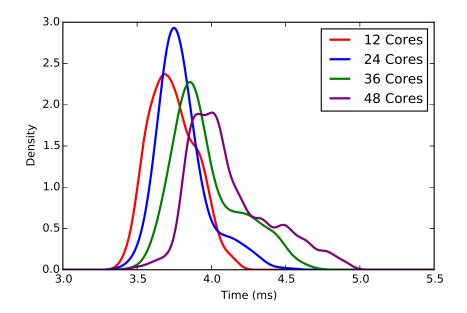

where A, B, and C are double precision matrices and  $\alpha$  and  $\beta$  are scalar multipliers. This task occurs in a number of dense linear algebra applications. In this case, we will examine the DGEMM task in the context of a Cholesky factorization and a tile-based implementation of DGEMM. In order to ensure all of the results were comparable, the DGEMM tasks being executed in the real workloads and the artificial benchmarks were all done with the same configurations. (TransA = Trans, TransB = NoTrans,  $m = 200, n = 200, k = 200, \alpha = -1.0, \text{ and } \beta = 1.0$ ) This ensures all of the workloads are identical and the only differences are the context in which they are executed. In the case of the Cholesky factorization, a matrix of size 5000 with a tile size of 200 was used. In the case of the DGEMM, A, B, and C are square matrices of size 2600 and a tile size of 200. The distribution of the DGEMM tasks in these two workloads are used as a baseline to evaluate the results of each of the synthetic benchmarks. These distributions are shown in red and blue in Figures 3.1, 3.2, 3.3, 3.4, 3.5, and 3.6.

The experiments were performed on two machines. One machine was composed of two 8 core Intel Xeon E5-2690 processors and 2 NUMA nodes. The second machine was equipped with four 12 core AMD Opteron 6180 SE processors and 8 NUMA nodes.

In order to evaluate the feasibility of deriving task timing models from synthetic benchmarks, a number of factors must be considered. Each of the benchmarks executes and collects the execution time of several iterations of the task. Presented here are six synthetic benchmarks fall into three primary categories as follows:

- Serial The Serial class of benchmarks is the most common and could be considered the naive implementation. In this case the memory is allocated and the tasks are computed. Assuming the "first touch" memory place policy, it is assumed the *A*, *B*, and *C* matrices will be initialized on the memory closest to the processor that will be performing the computations. This benchmark is generally unable to model the effects of NUMA architectures on the task timing. The results of the Serial benchmarks are shown in Figures 3.1 and 3.2.

- **NUMA** The NUMA class of benchmarks improves on the Serial benchmarks by accounting for the effects of non-local memory access during the computations. In this class of benchmarks, the process is initially bound to a single core from which the operands are allocated and initialized. This ensures the data will be placed on a single NUMA node based on the "first touch" rule. When the tasks are executed, they are performed on each of the cores in a sequential fashion. (i.e. the first n tasks are executed on the first core followed by the next n tasks on the second core etc.) The distribution derived from these benchmarks is often multimodal based on the distance between each of the processors and

the NUMA node containing the data. The results of the NUMA benchmarks are shown in Figures 3.3, 3.4.

• Threaded - The Threaded class of benchmarks aims to improve on the NUMA benchmarks by accounting for the memory contention that occurs during the real execution of a task-based workload. The Threaded benchmarks are multithreaded with each task explicitly bound to one core of the system. Each of the threads starts by allocating and initializing the operands in parallel. This ensures the operands are distributed across all of the NUMA nodes on the machine. If each thread only executed on the operands it was responsible for allocating, the benchmark would likely be artificially faster than expected because the tasks would never retrieve data from non-local memory. As a result, the operands are "shuffled" between the threads causing some of the operands to be in local memory while others are in non-local memory. Unlike the NUMA benchmarks, the Threaded benchmarks are executed in parallel to accurately stress the memory bandwidth as it would in a real task-based workload. The results of the Threaded benchmarks are shown in Figures 3.5, 3.6.

The synthetic benchmarks must also consider whether the operands are present in the cache at the time of execution. Operands not located in the cache must be retrieved from the main memory which increases the time to execute the task. In order to simulate the situation where the operands are in cache, the task is called repeatedly with the same operands. In order to simulate the situation where the data is not present in the cache, several operands are allocated and initialized prior to the execution of the tasks. Each task is called with a different operand ensuring the data must be retrieved from the main memory for each task.

The ability to account for warm cache and cold cache scenarios only complicates the design of an artificial benchmark. In the case of DGEMM, there are three primary operands (A, B, and C), raising the question of which operands should be in cache

**Table 3.1:** The 8 cache scenarios for A, B, and C in the synthetic DGEMM benchmarks. "IN" indicates the operand is in cache while "OUT" indicates the operand is out of cache.

| Α   | В   | С   |

|-----|-----|-----|

| IN  | IN  | IN  |

| IN  | IN  | OUT |

| IN  | OUT | IN  |

| IN  | OUT | OUT |

| OUT | IN  | IN  |

| OUT | IN  | OUT |

| OUT | OUT | IN  |

| OUT | OUT | OUT |

and which should not be in cache. With three operands that can be in cache or out of cache the number of possible benchmarks is 8 as shown in Table 3.1.

To complicate matters further, it is unlikely any of the operands will always be in cache. Perhaps a percentage of the time the operand is in cache. This can be simulated by slightly modifying the out of cache algorithm to use the same operand for some of the iterations while selecting a new operand for other iterations. It is also not possible at this time to consider a case where part of an operand is in cache. In the case of the Cholesky workload, there are different types of tasks being executed that can require varying amounts of memory bandwidth.

When the three classes are considered in conjunction with the numerous cache configurations it becomes a challenge to select the scenario that accurately reflects the distribution of task times in a real workload. Here we will examine just six of the many possible benchmarks.

The first two benchmarks are the cold cache and warm cache, Serial benchmarks. In these two benchmarks all of the operands are either in or out of cache and the data allocation, initialization, and task execution all occur on the same core. The results of these two benchmarks are shown in Figures 3.1 and 3.2. The cold cache benchmark is slower than the warm cache benchmark on both machines, but neither appears to accurately model the distribution of task times from the Cholesky factorization or the DGEMM workloads. On the Intel machine with two NUMA nodes, the synthetic benchmarks appear to "bound" the actual distributions while both appear to be faster than the real distributions on the AMD machine. This is likely due to the fact that the AMD machine has a greater number of cores and NUMA nodes that are not accounted for in the benchmarks.

Figures 3.3, 3.4 present the results of two NUMA benchmarks. The two benchmarks represent the case where all or none of the operands are in cache. When all of the operands are in cache the benchmark suggests artificially fast task time due to the decreased memory bandwidth requirements. The cold cache scenarios provide a multimodal distribution with modes corresponding to the distances between the processors and the memory containing the operands. Again, the benchmarks appear to "bound" the real distributions on the Intel machine while both benchmarks underestimate the task time on the AMD machine. This is likely due to the fact that the tasks are executed in serial and do not account for the memory contention present in a real workload.

Figures 3.5, 3.6 present the results for the warm and cold cache Threaded benchmarks. Again, the benchmarks on the Intel machine "bound" the actual distributions. On the AMD machine, however, the warm cache scenario underpredicts the execution time of the tasks, but the cold cache scenario appears to be much closer to the actual distribution of the task times.

The wide variety of benchmarks with varying accuracy makes synthetic benchmarks unappealing for building statistical models of the execution time for each task. As a result, data collected from the execution of a real workload provides the most accurate data for building task models.

**Figure 3.1:** Kernel Density Estimation curves for DGEMM including serial benchmark data sets. 2 x 8 Core Intel Xeon E5-2690

**Figure 3.2:** Kernel Density Estimation curves for DGEMM including serial benchmark data sets. 4 x 12 Core AMD Opteron 6180 SE

**Figure 3.3:** Kernel Density Estimation curves for DGEMM including NUMA benchmark data sets. 2 x 8 Core Intel Xeon E5-2690

**Figure 3.4:** Kernel Density Estimation curves for DGEMM including NUMA benchmark data sets. 4 x 12 Core AMD Opteron 6180 SE

**Figure 3.5:** Kernel Density Estimation curves for DGEMM including Threaded benchmark data sets. 2 x 8 Core Intel Xeon E5-2690

Figure 3.6: Kernel Density Estimation curves for DGEMM including Threaded benchmark data sets.  $4 \ge 12$  Core AMD Opteron 6180 SE

The results of runs shown in this paper were performed by linking with the Intel MKL library in order to obtain the best performance. As is common for large libraries, which require resource allocation, the MKL library initializes its internal state upon the first execution of a kernel and for each thread of execution. This may be easily observed as the first kernel on each thread will take significantly longer to execute than the following kernels. These extreme outliers can drastically affect the model fitting. For this reason, each of the threads is initialized with another call to the MKL library in order to ensure that this initialization is performed before the trace is collected. The same is done for the synthetic benchmarks as well.

#### Dense Linear Algebra Kernel Modeling

The sample problems examined here are Dense Linear Algebra applications. Their implementations are based on the PLASMA library where each high-level linear algebra routine is composed of several smaller tasks which can be scheduled based on their dependencies. Each of these tasks is a kernel belonging to any one of various classes of kernels, depending on the operation being performed. As mentioned above, each kernel of a given type does not have identical performance due, primarily, to the fact that each execution of the kernel will have different cache residencies. For example, one execution may have most of the data in cache while another execution has very little of the data in cache, which relates to, for example, task placement policies and to what extent the scheduler tracks data affinity.

In dense linear algebra, the kernels are most commonly described using the normal distribution of execution times, but similar distributions may also be used to model execution time. The simulation library currently supports normal, lognormal, and uniform time distributions as well as constant time models. In order to simplify the process of defining model configurations, a configuration file (based on a CSV format) is used to define the models for the simulator. These models can also be overwritten with a custom task time for a task. This will be described in greater detail in Section 4.3. Experience has shown that lognormal and normal distributions

have produced nearly identical simulation accuracy and can provide more accurate simulation than the uniform and constant task timing models.

#### 3.2.4 Task Execution Queue

In general, the dynamic scheduler maintains a dependence graph which is used to determine whether the dependences for a specific task have been satisfied. Whenever a task finishes its execution, the tasks waiting for the output of that task have a "waiting" dependence removed. Once all dependences have been removed for a task, the scheduler marks it to be available for execution.

In the case of simulated execution, the order in which these dependences are satisfied must be maintained in order for the simulations to be accurate. The key element of the simulation environment is the Task Execution Queue. This is the data structure ensuring the tasks that are currently in the execution state (Note: a task in the execution state is not actually computing the function it simulates) within the simulation maintain the proper completion order. When each task is executed in the simulation it already knows when it will end in the simulation based on the simulation clock time at the start time of the simulation and the expected execution time of the task based on a statistical model. In order to ensure the tasks (and implied dependencies) are completed (and released) in the same order, the tasks are released one at a time based on the order in the queue. The queue is ordered based on the simulated ending time of the tasks that are currently executing.

#### 3.2.5 Simulation Task Function

In order to use the simulation library, the developer simply replaces the calls to each computational kernel with a call to the simulated kernel. This simulated kernel requires an identifier as well as any handles or pointers that will create a dependence in the real execution of the algorithm. Although the memory is never accessed, the actual memory location in the process' address space is required in order to ensure all of the dependencies will be maintained. Furthermore, some schedulers perform copies of the data to deal with anti-dependences and real memory locations are required for such copies to succeed. The simulated tasks derive their execution time based on a random task time generated within a distribution provided in the simulation configuration file. The user also has the ability to specify a custom task time which will be described later. The simulated tasks are inserted into the task graph using the scheduler's API in an identical fashion to a real kernel.

The scheduler continuously maintains dependences and schedules each task accordingly. When a simulated kernel is executed, the simulation begins by checking the simulation clock to determine when the kernel is starting. Based on the kernel starting time and the estimated time of kernel execution (based on the kernel's model of completion time), the ending time can be obtained. The simulated kernel then acquires the lock on the Task Execution Queue and is added to the queue. The kernel information can now be added to the simulated trace and is ready to exit. However, the task must wait until it is at the front of the queue in order to allow the function to return. From the scheduler's perspective, the task is still executing until the function (which represents the task) returns. Before finishing, however, the simulated kernel must also update the global simulation clock to the completion time from the model distribution before the function returns.

#### 3.2.6 Scheduling Race Condition

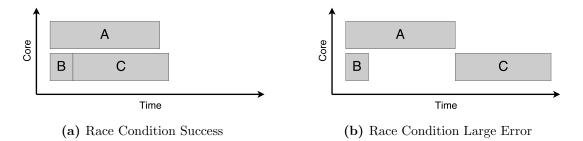

One of the challenging aspects of ensuring the correctness of the simulation stems from a possible race condition. The race condition can occur when a task is at the front of the Task Execution Queue while the scheduler is inserting new tasks. Each task starts by determining a start time by querying the simulation clock. Each task ends by updating the simulation clock. The race condition arises when a task attempts to complete while another task is determining what time it started in the simulation. If the new task gets the simulation clock before the update by another task, the results will be accurate. If, however, the other task completes and updates the clock before the new task can query the simulation time, the start time of the task will be incorrect. The magnitude of the error depends on the structure of the algorithm and the tasks involved.

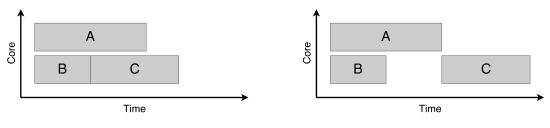

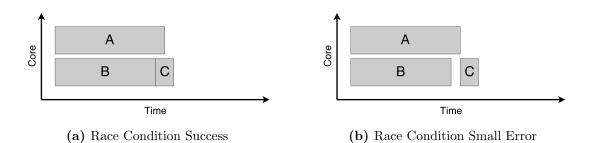

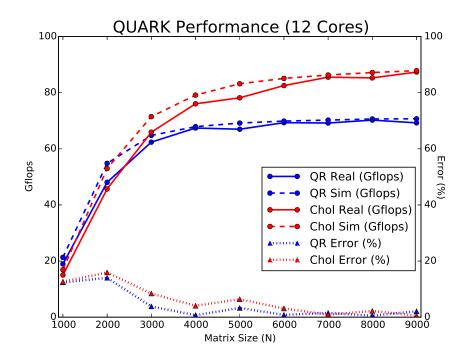

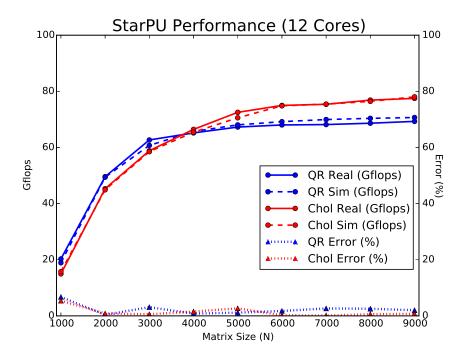

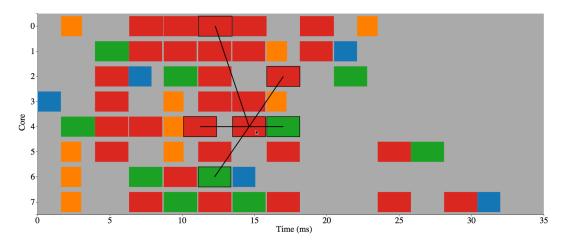

Figure 3.7 presents a more concrete example of the effects of this race condition. This simple workload includes three tasks and is performed on a two core system. Tasks A and B are independent and can be scheduled at the same time. Task C depends on data from B but is independent of Task A. Figure 3.7a represents what the actual execution of the workload would look like. Tasks A and B are scheduled on the two available cores. Once Task B completes, the scheduler recognizes that the data Task C is waiting for has been satisfied with the completion of Task B. As a result, the scheduler executes Task C on the second core of the system.